# GLOBAL INSTRUCTION SCHEDULING FOR MULTI-THREADED ARCHITECTURES

GUILHERME DE LIMA OTTONI

A DISSERTATION PRESENTED TO THE FACULTY OF PRINCETON UNIVERSITY IN CANDIDACY FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

RECOMMENDED FOR ACCEPTANCE BY THE DEPARTMENT OF COMPUTER SCIENCE

Advisor: David I. August

September 2008

© Copyright by Guilherme de Lima Ottoni, 2008.

All Rights Reserved

#### Abstract

Recently, the microprocessor industry has moved toward multi-core or chip multiprocessor (CMP) designs as a means of utilizing the increasing transistor counts in the face of physical and micro-architectural limitations. Despite this move, CMPs do not directly improve the performance of single-threaded codes, a characteristic of most applications. In effect, the move to CMPs has shifted even more the task of improving performance from the hardware to the software.

Since developing parallel applications has long been recognized as significantly harder than developing sequential ones, it is very desirable to have automatic tools to extract thread-level parallelism (TLP) from sequential applications. Unfortunately, automatic parallelization has only been successful in the restricted domains of scientific and data-parallel applications, which usually have regular array-based memory accesses and little control flow. In order to support parallelization of general-purpose applications, computer architects have proposed CMPs with light-weight, fine-grained (scalar) communication mechanisms. Despite such support, most existing multi-threading compilation techniques have generally demonstrated little effectiveness in extracting parallelism from non-scientific applications. The main reason for this is that such techniques are mostly restricted to extracting parallelism within local, straight-line regions of code. As observed in several limit studies, local regions of code contain limited parallelism, and control dependence analysis and multiple control units are necessary to extract most of the parallelism opportunities.

This thesis describes a general compiler framework for Global Multi-Threaded (GMT) instruction scheduling, i.e. to simultaneously schedule instructions from a global region of code to extract TLP for multi-threaded architectures. Our compiler framework is based on a Program Dependence Graph (PDG) representation, efficient graph partitioning algorithms, and novel multi-threaded code generation algorithms. Central to this framework are our multi-threaded code generation algorithms, which produce efficient code for arbitrary partitions of the PDG into threads. Based on this framework, three thread-partitioning

strategies for GMT instructions scheduling are proposed. The first one, called GREMIO, extends list-scheduling to target multi-threaded architectures and to operate on global code regions. The second technique, called Decoupled Software Pipelining (DSWP), extracts pipelined TLP from arbitrary loop nests. We also propose Parallel-Stage DSWP, an extension of DSWP that allows multiple threads to concurrently execute the same stage of the pipeline. These techniques are implemented in the VELOCITY compiler and evaluated on an accurate CMP simulator built on top of validated Itanium 2 core models. The experiments show that our techniques balance applicability and scalability differently, with each technique resulting in the best speedup in different scenarios. Overall, the results demonstrate the effectiveness of the proposed compilation techniques, with significant speedups on a number of real benchmark applications written in C.

#### Acknowledgments

First, I thank my advisor, David, for making this work possible in various ways. I thank David for the liberty of picking my research topic, and for believing in me throughout this journey. David's leadership inside the Liberty Research Group also enabled the good research infrastructure that made this work possible. His critical feedback certainly helped both shape and improve this work. I also appreciate his help to improve my English and oral-presentation skills. I also thank David for the financial support for my studies, which allowed me to focus on my research. Finally, I thank David for motivating me to work hard and to continuously try to improve the quality of this work.

This work would also be hardly possible without the support from my fellow Liberators. The VELOCITY compiler was written by a group of students, including myself, Spyridon Triantafyllis, Matthew Bridges, Neil Vachharajani, Easwaran Raman, and others. I am very grateful to these colleagues for helping build such a nice infrastructure to do compiler research. The highly accurate multiprocessor simulator used in this thesis' experiments was built by Ram Rangan, based on a validated uniprocessor simulator written by David Penry. The work in this thesis was partly motivated by an earlier work by Ram Rangan, Neil Vachharajani, and David August on manually parallelizing loops that traverse recursive data structures. The IMPACT compiler from the University of Illinois at Urbana-Champaign provided not only the front-end for our compiler, but also a credible infrastructure in which I originally implemented several of the ideas in this thesis. I also thank the various Liberators for listening to my research ideas, reading my paper drafts, and providing me with invaluable feedback. I am also grateful to the Liberators with whom I had the opportunity to exchange ideas and coauthor papers. I am particularly indebted to Thomas Jablin who, as the only English native speaker in my office for a while, I constantly bugged close to paper deadlines. Thomas also generously proofread this dissertation. Finally, I am indebted with the Liberators responsible for maintaining our computer systems, including Neil Vachharajani, Matthew Bridges, Thomas Jablin, and Arun Raman. Without their help and the Condor job-management system, the 100,000-hour simulation results presented in this thesis would not be possible.

I thank the members of my thesis committee, David August, Vivek Sarkar, Sharad Malik, Margaret Martonosi, and David Walker, for taking the time to participate in my committee. Their feedback have definitely improved the quality of this work. Particularly, I thank the readers in my committee, Vivek Sarkar and Sharad Malik. Vivek Sarkar provided me with very qualified and detailed comments on various technical aspects of this work. His large experience in this field also helped me better understand the relations and contributions of my work compared to previous research in this area. I thank Sharad Malik for reading this dissertation in the short period that was left to him.

I also thank the entire staff of Princeton, and of the Department of Computer Science in particular. Their professionalism really makes this such a great place to study and to do research. I especially thank Melissa Lawson who, as the highly effective Graduate Coordinator, makes all the bureaucracy so simple and allows us to completely focus on our studies.

My studies at Princeton have been financially supported by grants from Intel Corporation, National Science Foundation, and Gigascale Systems Research Center, graduate fellowships from the Intel Foundation and Princeton's School of Engineering and Applied Science (SEAS), and special awards from the Department of Computer Science and SEAS. I also thank Intel for the opportunities to do two Summer internships, which provided me not only great industrial research experience, but also funds to survive the grad-student life.

I am also indebted to the Brazilian people, who support the good public (free) educational system in Brazil. Without the background acquired at Juvenal Miller, CTI-FURG, FURG, and UNICAMP, I would not have reached this far.

I am very fortunate to have been born an raised in an extremely happy and fun family. The distance from my parents, Elias and Lúcia, and my siblings, Gustavo, Tatiana, and Frederico, definitely made my move to the United States harder. Fortunately, the Internet and Skype enabled our long weekend conversations that virtually reduced the distance between us and made me, for a couple of hours a week, feel as if I was back in Brazil.

Keeping sane while going through a Ph.D. program is probably impossible without the company of friends to help one relax and forget the work for a few hours a week. For that, I thank many friends, especially Desirée, Luis Fernando, Diogo, Letícia, Michel, Adriana, Diego, Marcio, Juliana, Renato, and others. Through some bottles of wine or a good *churrasco* (Brazilian barbecue), and speaking *um bom português (ou "gauchês")*, they helped me get the necessary breaks from my research. I also thank some of these friends and the rest of the guys who appeared for our joyful weekly *peladas* (soccer games) at Rutgers.

Finally, and most importantly, I thank my wife, Desirée. Her love, care, understanding, incentive, and company were invaluable to give me strength throughout not only the Ph.D. journey, but most of my life so far. I deeply thank her understanding of one of my lifetime dreams, which was to study in one of the best schools in the world. Her love and understanding made my dream possible, despite all the changes, uncertainties, challenges, and difficulties that this life's choice brought to both of us. I also thank her for the strength to face adverse real-life situations, for our two little angels, and for our hopefully coming baby. *Mori, eu te amo muito!!!*  "The difficulties were created to be overcome, and we must never give up until we are absolutely certain that we are incapable."

Sebastião P. Ottoni

For my precious wife Desirée

# Contents

|   | Abst | ract                                                    | iii |

|---|------|---------------------------------------------------------|-----|

|   | Ack  | nowledgments                                            | v   |

|   | List | of Tables                                               | xiv |

|   | List | of Figures                                              | XV  |

| 1 | Intr | oduction                                                | 1   |

|   | 1.1  | Coarse-Grained Thread-Level Parallelism                 | 4   |

|   | 1.2  | Fine-Grained Thread-Level Parallelism                   | 5   |

|   | 1.3  | Parallelism: Limits and Limitations                     | 9   |

|   | 1.4  | Our Approach                                            | 10  |

|   | 1.5  | Contributions                                           | 12  |

|   | 1.6  | Overview                                                | 14  |

|   |      |                                                         |     |

| I | Pro  | ogram Representation and Multi-Threaded Code Generation | 15  |

| 2 | Dep  | endence Graphs                                          | 17  |

|   | 2.1  | Data Dependence Graphs                                  | 17  |

|   | 2.2  | Control Dependence Graphs                               | 18  |

|   | 2.3  | Program Dependence Graphs                               | 20  |

| 3 | Mul  | ti-Threaded Code Generation                             | 22  |

|   | 3.1  | MTCG Algorithm                                          | 23  |

|    |      | 3.1.1    | Creating New CFGs' Basic Blocks       | 26 |

|----|------|----------|---------------------------------------|----|

|    |      | 3.1.2    | Moving Instructions to New CFGs       | 27 |

|    |      | 3.1.3    | Inserting Inter-Thread Communication  | 27 |

|    |      | 3.1.4    | Creating New CFGs' Arcs               | 33 |

|    | 3.2  | Correc   | ctness of the MTCG Algorithm          | 34 |

|    | 3.3  | Signifi  | icance                                | 37 |

| 4  | Inte | r-Threa  | ad Communication Optimizations        | 40 |

|    | 4.1  | Proble   | m Formulation                         | 42 |

|    | 4.2  | Optim    | izing a Pair of Threads               | 47 |

|    |      | 4.2.1    | Optimizing Register Communication     | 47 |

|    |      | 4.2.2    | Reducing Control Flow                 | 51 |

|    |      | 4.2.3    | Optimizing Memory Synchronizations    | 54 |

|    | 4.3  | Optim    | izing Multiple Threads                | 56 |

|    | 4.4  | Experi   | imental Evaluation                    | 59 |

|    |      | 4.4.1    | Experimental Methodology              | 59 |

|    |      | 4.4.2    | Experimental Results                  | 63 |

|    | 4.5  | Relate   | d Work                                | 68 |

|    | 4.6  | Signifi  | icance                                | 70 |

| II | Tł   | nread-   | Partitioning Techniques               | 72 |

| 5  | Glo  | bal List | -Scheduling-Based Thread Partitioning | 74 |

|    | 5.1  | GREM     | IIO Algorithm                         | 75 |

|    |      | 5.1.1    | Clustering Algorithm                  | 77 |

|    |      | 5.1.2    | Global Multi-Threaded List Scheduling | 79 |

|    |      | 5.1.3    | Handling Loop Nests                   | 83 |

|    |      | 5.1.4    | Putting It All Together               | 84 |

|   |      | 5.1.5     | Complexity Analysis                                   | 8  | 5 |

|---|------|-----------|-------------------------------------------------------|----|---|

|   | 5.2  | Experi    | mental Evaluation                                     | 8  | 6 |

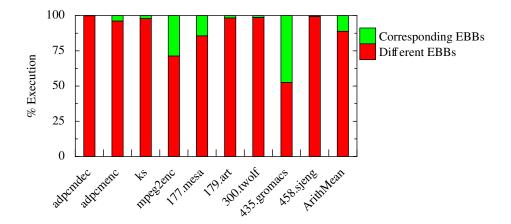

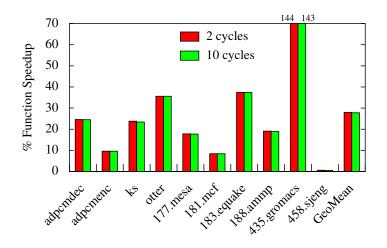

|   |      | 5.2.1     | Comparison to Local Multi-Threaded Scheduling         | 8  | 8 |

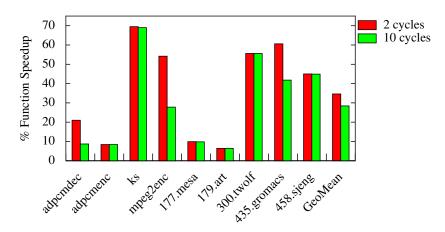

|   |      | 5.2.2     | Sensitivity to Communication Latency                  | 8  | 9 |

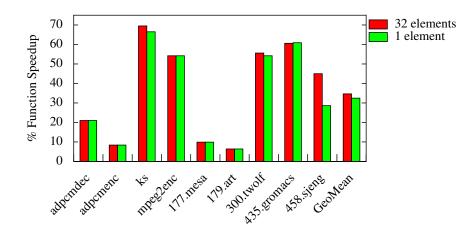

|   |      | 5.2.3     | Sensitivity to Queue Size                             | 8  | 9 |

|   | 5.3  | Relate    | d Work                                                | 9  | 0 |

|   | 5.4  | Signifi   | cance                                                 | 9  | 2 |

| 6 | Dec  | oupled    | Software Pipelining Thread Partitioning               | 9  | 3 |

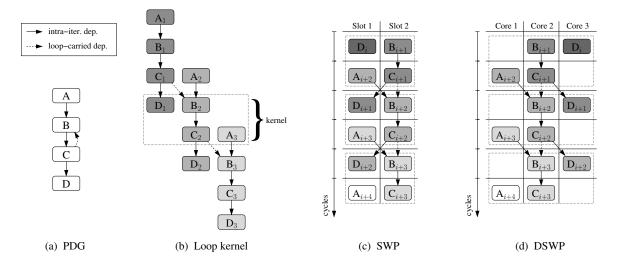

|   | 6.1  | DSWF      | PAlgorithm                                            | 9  | 7 |

|   | 6.2  | DSWF      | P Thread-Partitioning Problem                         | 10 | 1 |

|   |      | 6.2.1     | Problem Formulation and Complexity                    | 10 | 2 |

|   |      | 6.2.2     | Load-Balance Heuristic                                | 10 | 3 |

|   | 6.3  | Experi    | imental Evaluation                                    | 10 | 5 |

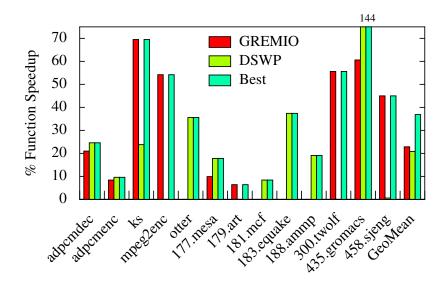

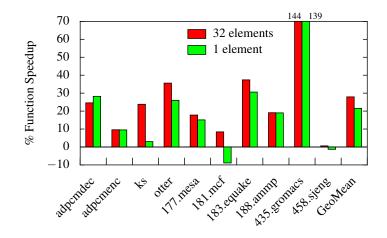

|   |      | 6.3.1     | Dual-Thread Results                                   | 10 | 5 |

|   |      | 6.3.2     | Comparison to GREMIO                                  | 10 | 6 |

|   |      | 6.3.3     | Sensitivity to Communication Latency                  | 10 | 7 |

|   |      | 6.3.4     | Sensitivity to Queue Size                             | 10 | 7 |

|   |      | 6.3.5     | Scalability                                           | 10 | 8 |

|   | 6.4  | Relate    | d Work                                                | 10 | 9 |

|   | 6.5  | Signifi   | icance                                                | 11 | 1 |

| 7 | Para | allel-Sta | age Decoupled Software Pipelining Thread Partitioning | 11 | 2 |

|   | 7.1  | Breaki    | ing Loop-Carried Dependences                          | 11 | 5 |

|   | 7.2  | PS-DS     | WP Partitioning                                       | 11 | 6 |

|   | 7.3  | Code (    | Generation                                            | 11 | 8 |

|   |      | 7.3.1     | Communication Insertion                               | 11 | 9 |

|   |      | 7.3.2     | Loop Termination                                      | 12 | 2 |

|   | 7.4               | Experimental Evaluation         |            |  |

|---|-------------------|---------------------------------|------------|--|

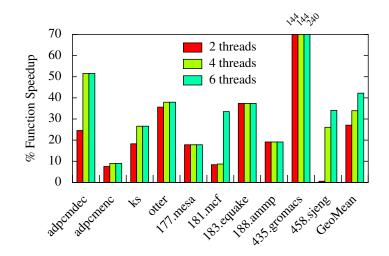

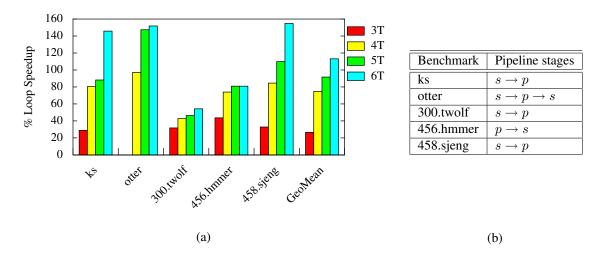

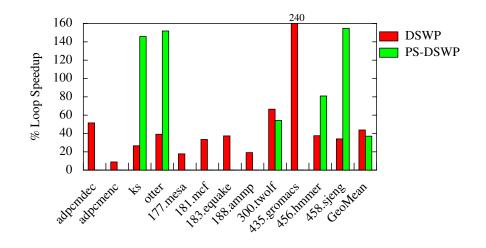

|   |                   | 7.4.1 PS-DSWP Results           | 123        |  |

|   |                   | 7.4.2 Comparison to DSWP        | 124        |  |

|   | 7.5               | Significance                    | 125        |  |

|   |                   |                                 |            |  |

|   |                   | nclusions and Future Directions |            |  |

| 8 | Con               | nclusions and Future Directions | 127        |  |

| 8 | <b>Con</b><br>8.1 |                                 |            |  |

| 8 | 8.1               |                                 | 127        |  |

| 8 | 8.1               | Summary                         | 127<br>130 |  |

# **List of Tables**

| 4.1 | Machine details.                         | 61 |

|-----|------------------------------------------|----|

| 4.2 | Selected benchmark functions             | 63 |

| 5.1 | Type of parallelism extracted by GREMIO. | 87 |

| 5.2 | Instruction scheduling space.            | 91 |

# **List of Figures**

| 1.1 | Performance trend of SPEC Integer benchmark suite on various machines                    |    |

|-----|------------------------------------------------------------------------------------------|----|

|     | released over time. Different versions of the benchmark suite were normal-               |    |

|     | ized using common machines. Source data from SPEC [99]                                   | 3  |

| 1.2 | Framework for global multi-threaded instruction scheduling                               | 12 |

| 2.1 | Example code in: (a) C, (b) low-level IR, (c) CFG, (d) post-dominance tree, and (e) PDG. | 21 |

| 3.1 | Example of the MTCG algorithm. (a) C source code; (b) original low-level                 |    |

|     | code; (c) partitioned PDG; and (d)-(e) resulting multi-threaded code                     | 25 |

| 4.1 | Simple example of the MTCG algorithm.                                                    | 42 |

| 4.2 | Example CFG illustrating the impossibility of statically placing communi-                |    |

|     | cations optimally.                                                                       | 44 |

| 4.3 | An example with loops                                                                    | 50 |

| 4.4 | An example including memory dependences.                                                 | 53 |

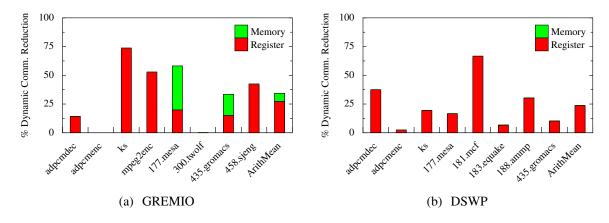

| 4.5 | Breakdown of dynamic instructions in code generated by the basic MTCG                    |    |

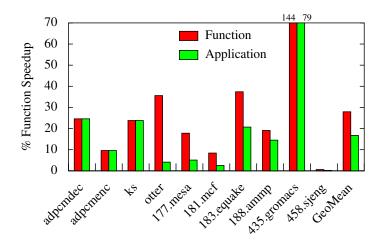

|     | algorithm (without COCO), for (a) GREMIO and (b) DSWP                                    | 64 |

| 4.6 | Reduction in the dynamic communication / synchronization instructions by                 |    |

|     | applying COCO, compared to the basic MTCG algorithm                                      | 65 |

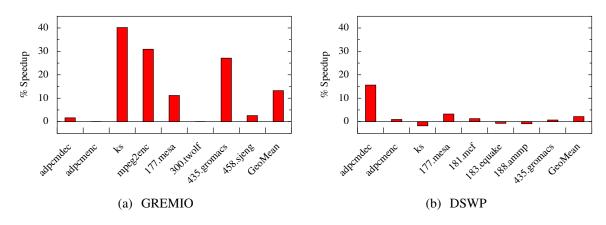

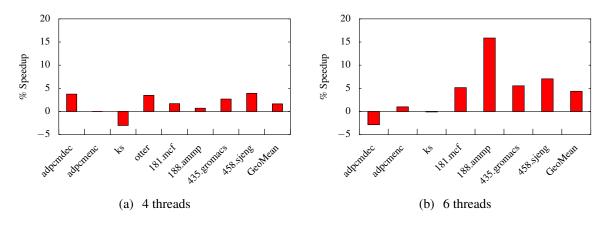

| 4.7 | Speedup of using COCO over code generated by the basic MTCG algorithm.                   | 65 |

| 4.8 | Speedup of using COCO over code generated by the basic MTCG algo-                  |

|-----|------------------------------------------------------------------------------------|

|     | rithm for DSWP with (a) 4 threads, and (b) 6 threads                               |

| 5.1 | Example code in: (a) C, (b) low-level IR, (c) CFG, and (d) PDG 76                  |

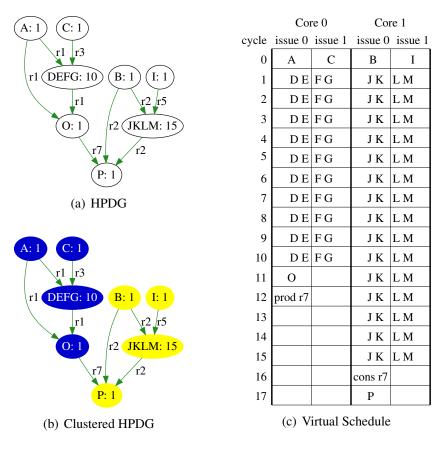

| 5.2 | Operation of GREMIO on the example from Figure 5.1                                 |

| 5.3 | HPDG tree for the PDG in Figure 5.1                                                |

| 5.4 | Resulting multi-threaded code                                                      |

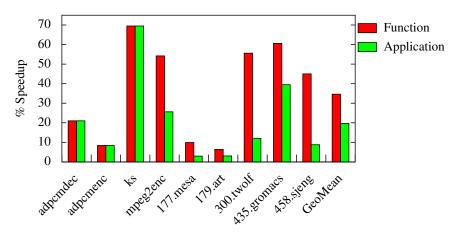

| 5.5 | Speedup of dual-thread GREMIO over single-threaded                                 |

| 5.6 | Percentage of execution on corresponding extended basic blocks                     |

| 5.7 | Speedup over single-threaded for different communication latencies 89              |

| 5.8 | Speedup over single-threaded for different size of queues                          |

| 6.1 | A simple example comparing Software Pipelining (SWP) and Decoupled                 |

|     | Software Pipelining (DSWP)                                                         |

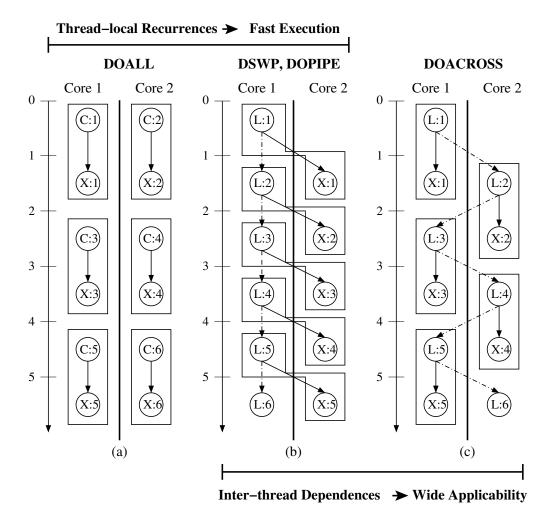

| 6.2 | Execution timelines for DOALL, DSWP, DOPIPE, and DOACROSS 96                       |

| 6.3 | DSWP example                                                                       |

| 6.4 | Speedups for dual-thread DSWP over single-threaded execution 105                   |

| 6.5 | Speedups for dual-thread GREMIO and DSWP over single-threaded exe-                 |

|     | cution                                                                             |

| 6.6 | Speedups for dual-thread DSWP over single-threaded execution, with dif-            |

|     | ferent communication latencies                                                     |

| 6.7 | Speedups for dual-thread DSWP over single-threaded execution, with dif-            |

|     | ferent queue sizes                                                                 |

| 6.8 | Speedups for DSWP over single-threaded execution                                   |

| 7.1 | Motivating example                                                                 |

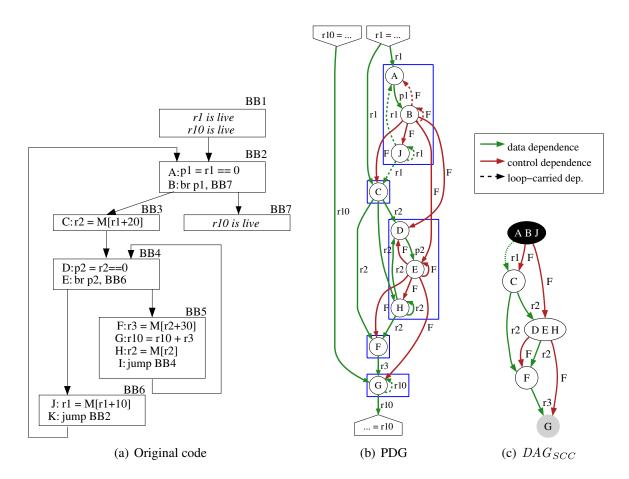

| 7.2 | (a) Low-level code, (b) PDG, and (c) $DAG_{SCC}$ for the example in Figure 7.1.115 |

| 7.3 | (a) Speedups for PS-DSWP over single-threaded execution. (b) Resulting             |

|     | pipeline stages (sequential or parallel)                                           |

| 7.4 | Speedups for PS-DSWP and DSWP using up to 6 threads, over single- |     |

|-----|-------------------------------------------------------------------|-----|

|     | threaded execution.                                               | 125 |

## Chapter 1

## Introduction

Since their invention, computers have been used for an increasing number of applications. Today, these uses range from embedded applications (e.g. car and aircraft control, voice processing in cell phones) to desktop applications (e.g. Internet browsing, gaming) to supercomputer applications (e.g. weather forecast, seismic simulation). This wide adoption of computers is a result of both their constant cost reduction and their continuous increase in performance. This work focuses on improving the performance of applications on modern computers.

For the vast majority of the applications, performance improvements have mainly been a result of two factors. First, and most importantly, processors have become faster due to improvements in the process technology. The clock rate of processors has improved from 5 KHz in the 1940s (ENIAC [111]) to 3 GHz in 2000s (Pentium 4 [45]). The second factor for increase in performance is the constant improvement in the processors' microarchitecture (e.g. caches and branch prediction) and accompanying compiler technology. Together, the effect of micro-architectural and compilation improvements is estimated to account for 40% increase in performance per year [10]. Besides these two main factors, in limited application domains that require extraordinary computing power and contain abundant parallelism (e.g. physical simulations), supercomputers consisting of multiple processors have been used to provide extra performance.

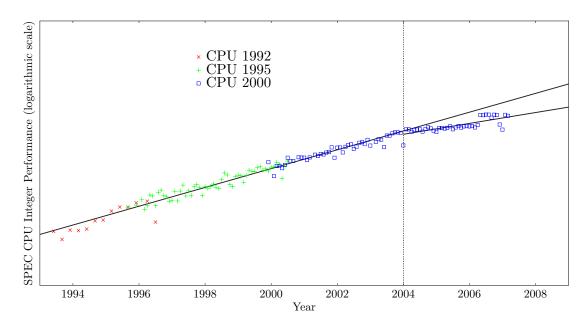

This long-lasting scenario for improving performance is now changing. Recently, the microprocessor industry has reached hard physical limits, including heat dissipation and power consumption, that are preventing faster clock rates. Furthermore, more aggressive micro-architectural techniques adversely affect these physical issues, both by requiring more complex, power-hungry hardware components and by adding logic to the critical path to execute instructions. Moreover, micro-architectural techniques generally provide diminishing returns. Therefore, neither clock rate nor micro-architectural techniques are contributing to significantly improve performance anymore. As a result, the performance of most applications is not increasing at the same pace it used to for several decades. Figure 1.1 illustrates this effect on three generations of the SPEC CPU Integer benchmark suite [99]. Each point in this graph represents a different machine. For each month in the x-axis, the best performance among the machines reported during this month is plotted. The different benchmark suites were normalized using common processors reported. The two different trend lines are linear regressions. The steepest line was computed using the processors released before 2004, and it represents the past performance trend. The other line was computed for processors released starting in 2004, and it represents the current performance trend.

The current reduction in the performance trend is a result of the aforementioned limitations in both clock frequency and micro-architecture. Since these were the two main sources of increase in performance, improving performance now lies on parallelism, which was the third and far less important source of performance for decades.

The good news is that parallelism is becoming cheaper. With Moore's Law's continuous increase in transistor count per chip [63], multi-core processors have become the norm. Multi-threaded and/or multi-core processors are found today even in desktops, laptops, and cell phones. These parallel machines are available in most systems, even if the users/applications do not fully utilize them. Furthermore, compared to traditional symmetric multi-processor (SMP) systems, the tightly integrated nature of single-chip multi-

Figure 1.1: Performance trend of SPEC Integer benchmark suite on various machines released over time. Different versions of the benchmark suite were normalized using common machines. Source data from SPEC [99].

processors brings the potential to exploit parallelism at finer granularities.

Despite the recent widespread availability of parallel machines, most existing applications do not benefit from this computation power. This fact is due to two main reasons: the lack of applications written in parallel languages, and the restricted applicability of automatic parallelization techniques.

Parallel applications can be obtained by having the programmer write applications in parallel programming languages. Nevertheless, most applications are still written in sequential languages for the ease of programming. In parallel programming paradigms, the programmer needs to reason about concurrency, communication costs, data locality and to worry about new problems caused by a large number of possible interleavings of multiple executing threads. Common concurrency bugs include data races, deadlocks, and livelocks. The great interest in tools to help detect these errors [20, 25, 27, 61, 94] is a testament to their commonality, difficulty, and cost. Given the higher costs of development and maintenance of parallel programs, from a software engineering perspective, it is definitely preferable to utilize sequential programming models.

Even if written in sequential paradigms, applications can potentially be translated into parallel codes. This can be achieved with the assistance of automatic tools, especially compilers. Unfortunately, however, automatic parallelization has only been successful in restricted application domains, mostly where data parallelism is abundant. In particular, automatic parallelization has been effective for scientific and media applications. For more general application domains, these techniques have not been able to extract useful parallelism. Particularly, the presence of irregular memory accesses (as in linked data structures) and intensive and arbitrary control flow render inapplicable most of the compiler parallelization techniques proposed over the last several decades.

In the next two sections, we briefly introduce some of the previous work on extracting TLP at both coarse and fine granularities. This overview helps understand the limitations of these techniques, thus putting in context and motivating our work. We then introduce our approach for TLP extraction and summarize the contributions of this thesis.

#### **1.1 Coarse-Grained Thread-Level Parallelism**

The great majority of the automatic parallelization techniques have focused on extracting coarse-grained parallelism at the loop level. These techniques typically exploit parallelism among different iterations of a loop whose iterations are all independent. Such loops are known as *DOALL loops* [2, 115]. The challenges in exploiting DOALL parallelism come from two complementary alternatives: (a) *analyzing* a loop nest to prove that its iterations are independent; and (b) *transforming* a non-DOALL loop nest into an equivalent DOALL one. Many techniques have been proposed to address both alternatives, including the GCD and Omega tests, polyhedral methods, loop skewing, and loop distribution [2, 115]. Compiler frameworks based on these techniques can generally find reasonable amounts of parallelism in regular scientific applications. In this application domain, programs typically contain counted loops, very little control flow, and regular array-based memory accesses.

However, outside the scientific computation domain, these techniques are rarely applicable. The reasons for this are mainly the large amount of irregular pointer-based memory accesses, uncounted loops, and control flow. These characteristics typically create interiteration (or loop-carried) dependences that are very hard, if not impossible, to eliminate.

In the presence of loop-carried dependences, one notable loop-parallelization technique has been proposed, called DOACROSS [22, 78]. With DOACROSS, loop iterations are executed in multiple processors in a round-robin fashion. To respect loop-carried dependences, synchronization primitives are inserted in the code, such that instructions in one iteration wait for their dependent instructions in the previous iterations to complete. Despite some success, the benefits of DOACROSS are generally limited by two factors. First, the number and position of loop-carried dependences lead to synchronizations in the code that limit the amount of parallelism. Second, by dividing the loop iterations among the processors in a round-robin fashion, DOACROSS inserts the synchronizations in the critical path to execute the loop. In other words, the cost of synchronization is paid between every pair of consecutive iterations, essentially multiplying the synchronization cost by the number of iterations of the loop. Together, these two issues generally negate the benefits of DOACROSS. However, DOACROSS has found applicability when combined with speculation, in techniques generally known as thread-level speculation (TLS) [9, 47, 98, 101, 106, 120]. Unfortunately, even with the support of speculation, the amount of parallelism obtained by these techniques has been limited, hardly justifying the complex hardware support necessary to keep the overhead of these techniques tolerable.

#### **1.2 Fine-Grained Thread-Level Parallelism**

Given the difficulty of finding coarse-grained parallelism in most applications, a few researchers have investigated the possibility of extracting fine-grained thread-level parallelism. The potential of exploiting parallelism at finer granularities is enabled by multi-core processors. Compared to traditional symmetric multi-processors (SMPs), there are two key differences that enable fine-grained parallelism in multi-core processors. First, there is the possibility of communicating directly between the cores, without having to go off-chip. This can provide a much higher communication bandwidth. Second, there is the possibility to integrate specialized hardware mechanisms into the chip, so as to lower the inter-core communication overheads. In this section, we give an overview of such communication mechanisms, as well as the proposed compilation techniques to exploit them.

A notable example of on-chip inter-core communication mechanism is the *scalar operand network* in the RAW processor [104, 110]. This mechanism consists of a programmable mesh inter-connect among the cores. Associated with each core, there is a routing coprocessor. To the software, the scalar operand network can essentially be abstracted as a set of hardware queues for scalar inter-core communication. Each core communicates with the other ones through its router. The accesses to the communication queues are encoded as reads and writes to specialized registers. For this reason, RAW's hardware queues are called register-mapped queues.

The key component of RAW's C compiler (RAWCC) is its instruction scheduler [59, 60]. For such spacial architecture, it is necessary to schedule instructions in both time and space (cores). Furthermore, the scheduler must also generate the necessary communications to satisfy inter-core dependences. The space-time scheduling approach used in the RAWCC compiler works as follows. For each basic block in the program, the *basic block orchestrator* partitions the instructions among the cores, using a space-aware variation of list scheduling [35]. Later, communications are generated to implement inter-core dependences. The basic block orchestrator processes each basic block independently: the assignment of instructions to cores in one basic block does not affect the assignment for other basic blocks. The coordination of the control flow among the cores is implemented using *asynchronous branching*. In this approach, the core containing the branch that ter-

minates the basic block broadcasts the direction of the branch to all other cores through the hardware queues. Upon receiving the branch direction, the other cores mimic the same branching behavior. With this technique, all cores essentially follow a control-flow graph that is isomorphic to the original one, and each core executes a subset of the original program's instructions. As such, this approach basically utilizes multiple cores/threads to exploit *instruction-level parallelism* inside each basic block. For this reason, we call this a *local multi-threaded (LMT) instruction scheduling* technique. The results reported for this technique show that it hardly matches the parallelism obtained by an aggressive outof-order processor [59].

Inter-core hardware queues have also been employed in *decoupled access-execute* processors [97]. In these processors, one core is dedicated to performing memory accesses, while another core executes the remaining instructions. The idea behind these processors is to try to decouple the execution of the non-memory-related instructions from the memory accesses, hopefully hiding the memory latencies. To implement the dependences between these two sets of instructions, two classes of scalar hardware queues are used. One class of queues is used to communicate scalar operands that either feed or result from memory instructions. The other is a *branching queue*, which is used to send the branch results from the execute core to the access core, so that the latter can follow the same execution path as the former. This compilation technique is classified as *LMT instruction scheduling*, since it essentially exploits parallelism inside basic blocks, with both threads executing all basic blocks in the program [88]. Experimental evaluations of decoupled access-execute architectures showed very little benefits, sometimes resulting in slowdowns because of the communication overhead and cyclic dependences between the threads [88].

Another hardware mechanism to implement inter-core scalar communication is the *synchronization array* [85]. In this mechanism, the processor's instruction set architecture (ISA) is extended with two new instructions, produce and consume, which respectively send and receive a scalar value through a given hardware queue. In [85], this hardware mechanism was used to support the parallelization of loops that traverse recursive/linked data structures. These loops were manually partitioned into two threads, one executing the data structure traversal, and the other executing the loop body. Similar to the decoupled-access-execute work, the idea was to hide the memory access latencies, which can be quite expensive in traversals of linked data structures due to the lack of locality. Unlike decoupled access-execute, however, reasonable speedups for selected pointer-intensive benchmarks were obtained in [85]. The key to their success was that, by creating a unidirectional flow of dependences between the threads, truly decoupled execution was achieved. This thread partitioning scheme, which produces *pipelined multi-threading*, was coined *Decoupled Software Pipelining* (DSWP). In this thesis, we propose general code partitioning and code generation algorithms that are able to extract an arbitrary number of threads from general loop regions (not only recursive data structure traversals) that exploit pipelined multi-threading. In fact, the techniques proposed in this thesis are even more general, not being limited to pipelined multi-threading.

Several alternatives to the synchronization array mechanisms were investigated with the goal of reducing the hardware costs for pipelined multi-threading [84]. As an interesting design point, we observed that the communication queues can be implemented through shared memory, for a small performance penalty. This not only reduces the hardware costs, but it also facilitates virtualization. To obtain good performance through shared memory, however, two hardware changes are still necessary. First, blocking produce and consume instructions are usually needed to avoid the costs of implementing synchronization in software. Second, it is necessary to change the cache coherence protocol to perform *forwarding of cache lines* used to implement the queues. By having a cache line forwarded from the producer core when it becomes full, stalls to access the queues in the consumer core are eliminated.

#### **1.3** Parallelism: Limits and Limitations

The previous sections described the main efforts on automatically exploiting parallelism. Despite the lack of success of automatic parallelization techniques, several limit studies have shown that even applications known as hard-to-parallelize have large amounts of parallelism [56, 108]. However, these limit studies are generally performed by execution-trace analysis, and they give very little insight on how to extract such parallelism.

So, the interesting question that arises is: what prevents such parallelism from being achieved by the hardware and/or the compiler? This is prevented by several limitations both in the hardware and in the compilers. We first describe the limitations of the hardware. Even with aggressive out-of-order execution, branch prediction, and large instruction windows, the processors still have fundamental limitations. In particular, processors only see the stream of dynamic instructions that actually execute. As a result, they are unable to detect merge points in a program's control-flow graph and to understand true control dependences. This results in hardware techniques being overly conservative in case of branch mispredictions, squashing even instructions that are not dependent on the branch. This fundamentally prevents a processor from extracting multiple threads of execution from a single program thread.

There are also several limitations that prevent compilers from automatically extracting parallelism, as we pointed out in [77]. Most importantly, parallelism is not very regular, rarely matching the DOALL and DOACROSS patterns that are implemented in many parallelizing compilers, such as the Intel Compiler [46], IBM's XL compiler [43], SUIF [38], and Parascope [18]. Compilers focusing on fine-grained TLP, such as RAWCC [59, 60], have tried to address this issue by looking at more irregular parallelism. However, these techniques have their own limitations. By fully replicating the control flow in all threads, they only exploit *local* parallelism. As such, local multi-threading instruction scheduling techniques essentially have the same limitations as the hardware: the inability to exploit parallelism across independent control regions to truly benefit from multiple threads of execution. As pointed out by Lam et al. [56], it is key to overcome these two limitations in order to extract reasonable amounts of parallelism. This brings another obstacle identified in [77] that traditionally inhibits parallelizing compilers: the scope of parallelization. To find most parallelization opportunities, it is generally necessary to look for parallelism across large regions of code, possibly inside an entire procedure or even across the whole program. Another parallelization obstacle is analyzing memory dependences. Statically determining precise memory aliasing is, in fact, a fundamental limitation [57, 80]. One way to get around this limitation is to rely on *speculation*. With speculation, certain dependences can be ignored, as long as run-time mechanisms to detect and recover from mis-speculations are available.

More recently, another fundamental limitation of automatic parallelization was identified in [10]. This work demonstrated that significantly more parallelism can be unlocked by changing a program's output by another, equivalently good output. However, benefiting from these opportunities clearly requires the programmer's intervention in order to convey the cases where this is valid. To enable these opportunities, simple source-code annotations were proposed in [10]. These annotations were shown to work very well in combination with the techniques proposed in this thesis.

#### **1.4 Our Approach**

The goal of this work is to design techniques to overcome the main aforementioned limitations of previous automatic parallelization techniques, so as to uncover some of the potential suggested by various limit studies. The general approach proposed in this work exploits fine-grained thread-level parallelism. To achieve so, this work generalizes instruction scheduling techniques to target multi-threaded architectures. Since most applications contain lots of control flow, a key goal in this work was to design techniques that look for parallelism in large code regions, beyond extended basic blocks<sup>1</sup> and inner loops. These

<sup>&</sup>lt;sup>1</sup>An extended basic block (EBB) is a sequence of instructions with a single entry (the first instruction) and potentially multiple exits.

techniques typically operate at outer loops or entire procedures, thus being classified as GMT instruction scheduling [72].

To represent the program region being scheduled, we use a variation of the *Program Dependence Graph* (PDG) [29]. The PDG is an elegant representation that has some important properties. First, it encodes all the program dependences that need to be preserved to keep the program's semantics [40, 91]. Second, the PDG can be built for low-level code, even at the assembly level. This property is important for the extraction of fine-grained parallelism, which is better performed in a compiler's back-end.

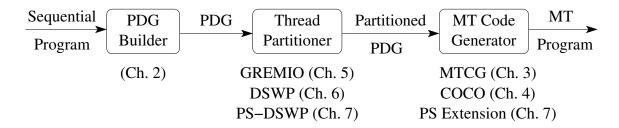

The approach for GMT instruction scheduling proposed in this thesis is very general. One of its key properties is the separation of concerns into *thread partitioning* and *code generation*, as illustrated in Figure 1.2. These two components are interfaced through a *partitioned PDG* representation. This design allows a thread partitioning algorithm to operate on an abstract, dependence-centric representation, the PDG, in order to find parallelism. By partitioning the PDG nodes among different blocks (threads), a partitioner exposes thread-level parallelism. Such approach enables different thread partitioning algorithms to be easily integrated into the same framework. From the partitioned PDG, multi-threaded code is generated. The multi-threaded code consists of the original instructions in the code, plus communication and synchronization instructions inserted to enforce all inter-thread dependences.

The framework proposed in this thesis preserves the order among all instructions assigned to the same thread. This design simplifies not only the interface between thread partitioning and code generation, but also the code generation algorithms described in this work. We rely on traditional single-threaded instruction scheduling to obtain a better ordering of the instructions in each thread, by taking into account the details of the target cores. However, this creates a phase-ordering problem because the extraction of parallelism is tackled independently in two different phases of the compilation. This problem is aggravated because single-threaded instruction schedulers are typically unaware of

Figure 1.2: Framework for global multi-threaded instruction scheduling.

inter-thread communication and thread-level parallelism. However, this problem can be mitigated by making the single-threaded instruction scheduler aware of inter-thread communication primitives, by giving special scheduling priorities to these primitives.

The techniques proposed in this thesis are *non-speculative*, and they require no special hardware support. Nevertheless, given the granularity of the parallelism typically found in applications, simple hardware mechanisms to reduce the overheads of inter-thread communication and synchronization can be very beneficial. Examples of such hardware mechanisms include synchronization arrays [84, 85] and scalar operand networks [104]. As mentioned in Section 1.2, these mechanisms have been previously proposed to support other fine-grained TLP approaches.

#### **1.5** Contributions

In summary, the main contributions of this thesis are:

The design and implementation of a general framework to perform global instruction scheduling for multi-threaded architectures [72, 74, 76]. This framework separates concerns into thread partitioning and code generation, thus providing great flexibility that enables various global scheduling algorithms to be easily implemented. This framework has been implemented both in the IMPACT [96] and in the VELOC-ITY [105] compilers, and it has been used to support a few research efforts on GMT instruction scheduling [10, 72, 73, 74, 76, 77, 81, 82, 83, 109].

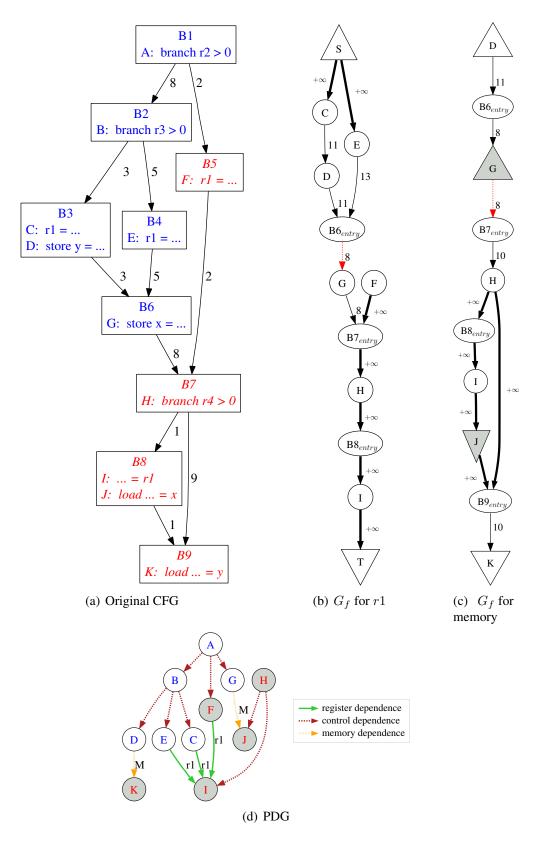

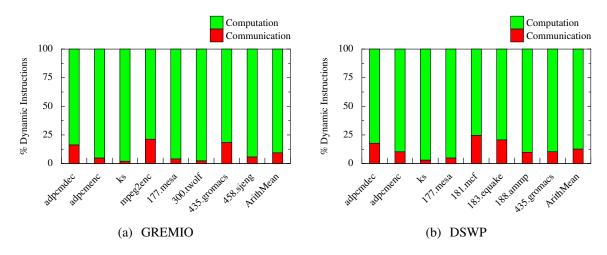

- 2. Algorithms to generate efficient multi-threaded code for arbitrary code partitions [73, 74]. The proposed *multi-threaded code generation* (MTCG) algorithm allows an arbitrary partition of PDG nodes to threads, and it produces code that does not replicate the entire control-flow graph for all produced threads. This is key to truly exploit parallelism across different control regions. In order to implement inter-thread dependences, the MTCG algorithm inserts communication and synchronization primitives. While the basic MTCG algorithm [74] is somewhat naïve in how it inserts communication primitives in the code, we also propose more advanced algorithms to obtain a better placement of these primitives. This communication optimization framework, called COCO [73], is based on novel thread-aware data-flow analyses and graph mincut algorithms, and it simultaneously optimizes all types of inter-thread dependences (control, register, and memory).

- 3. Algorithms to partition instructions into threads in order to expose thread-level parallelism. Based on the proposed compiler framework for GMT instruction scheduling, this thesis describes partitioning algorithms that extend single-threaded instruction scheduling techniques to generate TLP. More specifically, these thread-partitioning techniques are:

- (a) A list-scheduling-based partitioner, called GREMIO [72].

- (b) A Decoupled Software Pipelining (DSWP) thread partitioner [74, 76, 77].

- (c) An extension of DSWP that enables parallel stages in the pipeline, called Parallel-Stage Decoupled Software Pipelining (PS-DSWP) [77, 81]. (This technique is the result of a collaboration with Easwaran Raman.)

- Correctness proofs of the proposed algorithms. Given the design of our framework, the correctness of the generated code only depends on the code generation algorithms (MTCG and COCO).

5. Implementations and experimental evaluations of all the proposed techniques, which were implemented in the VELOCITY compiler [105].

#### 1.6 Overview

This dissertation is organized as illustrated in Figure 1.2, and it is divided in two parts. In Part I, which consists of Chapters 2 through 4, we describe the program representation and multi-threaded code generation algorithms. More specifically, Chapter 2 describes the variation of the program dependence graph we use. In Chapter 3, we describe the basic multi-threaded code generation (MTCG) algorithm, and we present the COCO communication optimizations in Chapter 4. In Part II, consisting of Chapters 5 through 7, we present the thread-partitioning techniques. Chapter 5 describes the list-scheduling-based partitioner (GREMIO). The Decoupled Software Pipelining (DSWP) partitioner is described in Chapter 6, while the Parallel-Stage DSWP extension is presented in Chapter 7. Chapter 8 presents the conclusions of this work and provides directions for future research on global multi-threaded instruction scheduling and code optimizations in general.

# Part I

# **Program Representation and**

# **Multi-Threaded Code Generation**

This part describes the program representation and general multi-threaded code generation algorithms. In Chapter 2, we describe the central program representation that we use in this work. This intermediate representation is a variation of the program dependence graph (PDG), and it can be built for arbitrary code, even at the machine level. The PDG representation serves as the interface between the thread partitioning techniques described in Part II and the code generation algorithms described in this part.

In Chapter 3, we describe our general multi-threaded code generation (MTCG) algorithm. This algorithm produces efficient and correct multi-threaded code for an arbitrary partition of the PDG nodes into threads. A key property of MTCG is that it does not replicate the control flow entirely in all threads. This property is key to enable truly thread-level parallelism. To the best of our knowledge, the MTCG algorithm is the first method to satisfy this property and to support arbitrary control flow and thread partitions. Furthermore, our MTCG algorithm is elegant and simple to implement.

The basic MTCG algorithm described in Chapter 3 uses a simple strategy to determine the program points where inter-thread communications are inserted. In Chapter 4, we describe a general framework, called COCO, to improve the placement of inter-thread communications. COCO improves the performance of the resulting code both by reducing the number of inter-thread communications and by eliminating synchronization points that prevent parallelism.

## Chapter 2

## **Dependence** Graphs

Dependence graphs are a traditional form of representing dependences among statements or instructions in a program. In this chapter, we introduce various forms of dependence graphs proposed in the literature and describe the variation used in this work.

#### **2.1 Data Dependence Graphs**

Data dependence graphs are a basic representation of dependences among instructions or statements of a program. In data dependence graphs, each vertex represents an instruction (or statement) in the program, and directed arcs specify data dependences between instructions. At a low-level representation, data dependence arcs can take two forms: either (virtual) register<sup>1</sup> data dependences or memory data dependences. Furthermore, data dependences can be of three kinds, depending on whether the involved instructions read from or write to the data location: *flow dependence*, which goes from a write to a read; *anti-dependence*, which goes from a read to a write; and *output dependence*, which goes from a write [54]. Register data dependences can be efficiently and precisely computed through data-flow analysis. For memory data dependences, compilers typically

<sup>&</sup>lt;sup>1</sup>In this dissertation, we assume a low-level IR with virtual registers, which may correspond to either temporaries emitted by the compiler or to program variables that can be promoted to physical registers [19]. We generally omit the word *virtual* in the text.

rely on the results of static memory analyses to determine loads and stores that may access the same memory locations. Although computationally much more complicated, practical existing pointer analysis can typically disambiguate a large number of non-conflicting memory accesses even for type-unsafe languages like C (e.g. [15, 36, 70]). Inter-procedural pointer analyses typically compute a summary of the memory accesses per function. With such information, complete memory data dependences can be computed not only between loads and stores, but also involving function calls.

Many memory analysis techniques have also been proposed for regular, array-based memory references [2, 115]. These analyses require a high-level intermediate representation, with explicit array accesses. With these techniques, it is possible to refine dependence arcs involving array accesses in loop nests with dependence distance vectors. Although these techniques are very important for array-based, scientific applications (typically written in FORTRAN), they are not so applicable to more irregular applications (typically written in C). For this reason, we do not use such memory analyses in most of this work.

Data dependence graphs are generally employed in scheduling and parallelization techniques allowing only very primitive or no forms of control flow. Such uses include instruction scheduling of basic blocks or inner loops with a straight-line body [65], and the vectorization and parallelization of simple inner loops [2].

#### 2.2 Control Dependence Graphs

For techniques that operate beyond straight-line code (basic block) boundaries, the notion of *control dependences* becomes relevant. An instruction (or statement) X controls an instruction Y if, depending on the direction taken at X, Y must execute along one path and may not execute along another path. Similar to data dependences, control dependences among the statements or instructions of a program can be represented as arcs in a directed graph.

Different notions of control dependence exist. For structured programs, the syntaxbased notion of control dependences is applicable [54]. At this level, a statement is control dependent on its closest enclosing control construct. Although very natural and easy to compute, this definition of control dependence is not applicable to unstructured programs (containing gotos, breaks, and continues) or even to structured programs after going through traditional compiler optimizations [1, 4, 17, 65].

Ferrante et al. [29] generalized the notion of control dependence to arbitrary controlflow graphs.<sup>2</sup> Their graph-based definition, which is based on the post-dominance relation [65], enables control dependences to be computed for low-level program representations. For this reason and some of its key properties, we use Ferrante et al.'s definition of control dependence in this work.

**Definition 1** (Control Dependence (Ferrante et al. [29])). *Let G* be a CFG, and X and Y two nodes in G. Y is control dependent on X iff:

- 1. there exists a directed path P from X to Y with any Z in P (excluding X and Y) post-dominated by Y; and

- 2. X is not strictly post-dominated by Y.

Cytron et al. [23] proposed an efficient algorithm to compute control dependences according to this definition.

To deal with the possibility of calling a function that may not return (e.g. because it may call exit in C), some extra control dependences are necessary. To properly compute control dependences in this case, auxiliary control-flow arcs are drawn from the instructions calling such possibly non-returning functions to the program's *END* node.<sup>3</sup> With these arcs inserted, control dependences are computed normally using standard algorithms [23, 29].

$<sup>^{2}</sup>$ In fact, Ferrante et al. [29] definition is restricted to control-flow graphs where all nodes can reach the *END* node.

<sup>&</sup>lt;sup>3</sup>Auxiliary control-flow arcs can also be used to model other non-explicit control transfers, such as exceptions.

In the resulting control dependences, some instructions will now be dependent on these function-call instructions. We name these dependences *call-exit control dependences*.

## 2.3 **Program Dependence Graphs**

Dependence graphs including both data and control dependences are generally called *Pro*gram Dependence Graphs (PDGs) [29, 54]. Compilers widely use PDGs as an intermediate representation due to several important properties. In particular, using syntax-based control dependences, Horwitz et al. [40] proved the *Equivalence Theorem*. According to this theorem, two programs with the same PDG are equivalent. Later, Sarkar [91] proved a similar result for PDGs using control dependences according to Definition 1.

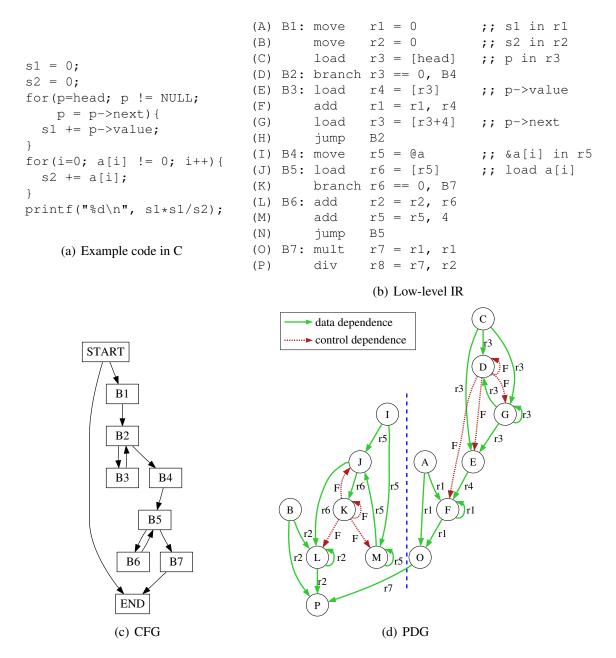

Traditionally, PDGs contain two kinds of nodes [29]: regular nodes, representing statements/instructions, and region nodes, representing a control-equivalent region of the program. In this work, however, we opted to have only regular nodes. Control dependence arcs are drawn directly from branch instructions to the dependent instructions. As will be clear in the following chapters, this allows a more homogeneous treatment of the PDG, since all its node represent actual instructions in the program.

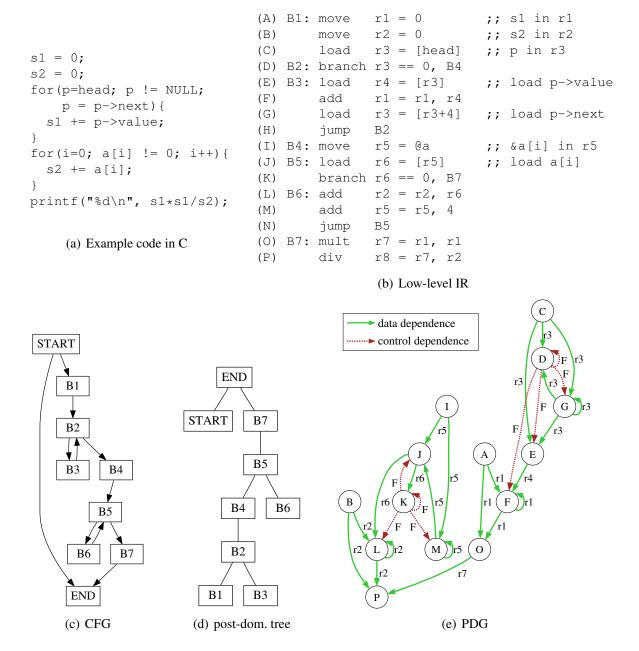

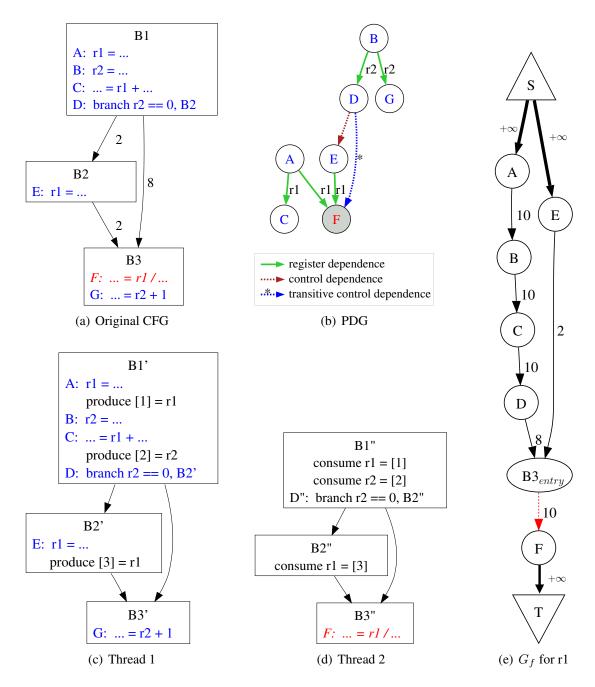

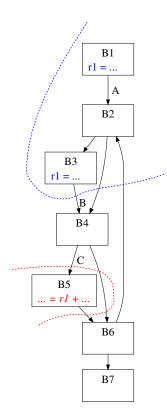

As an example, consider the C code in Figure 2.1(a), with corresponding low-level representation in Figure 2.1(b). Figures 2.1(c)-(e) illustrate the corresponding CFG, post-dominance tree, and PDG. In Figure 2.1(e), solid arcs represent data dependences, which are all register dependences in this example, and dotted arcs represent control dependences. Register dependence arcs are labeled with the register involved in the dependence, while control arcs are labeled with the branch direction that causes the dependent instruction to execute.

In the PDG used in most of this work, only true (flow) register dependences are included. Since there is no ambiguity in register accesses, renaming can generally be used to eliminate output and anti-dependences. As described in Chapter 3, our algorithms take into account these dependences only when they are necessary.

Figure 2.1: Example code in: (a) C, (b) low-level IR, (c) CFG, (d) post-dominance tree, and (e) PDG.

## Chapter 3

# **Multi-Threaded Code Generation**

As discussed in Section 1.4, one of the key enablers of GMT instruction scheduling is the ability to generate efficient code for a given code partition. In this chapter, we describe our general multi-threaded code generation algorithm, called MTCG [74].

There are several requirements for a code generator to support GMT instruction scheduling. First, in order to handle global code regions, it is desirable to use a PDG representation. As discussed in Chapter 2, respecting the dependences in a PDG guarantees the preservation of the program's semantics. Another requirement of a general multi-threaded code generator is the ability to handle *arbitrary code partitions*. By code partition, we mean an assignment of instructions to threads.<sup>1</sup> Handling arbitrary code partitions is important to support different thread partitioning algorithms, and it is central to provide the separation of concerns into partitioning and code generation mentioned in Section 1.4. A third requirement of a multi-threaded code generation algorithm is to be able to produce efficient code. To achieve this, it is particularly important to avoid replicating the control flow as much as possible, which is the main drawback of LMT scheduling techniques (Section 1.2). The MTCG algorithm proposed in this work was designed to meet all the above requirements. In Section 3.1, we describe the MTCG algorithm. Section 3.2 presents the proof of correctness of the algorithm.

<sup>&</sup>lt;sup>1</sup>A code partition does not specify the order among the instructions in each thread.

## **3.1 MTCG Algorithm**

This subsection describes the MTCG algorithm [74], whose pseudo-code is illustrated as Algorithm 1. This algorithm takes as input a program dependence graph (*PDG*) for the code region being scheduled and a given partition ( $\mathcal{P}$ ) of its nodes (instructions) into threads. Furthermore, for simplicity, we assume here that a control-flow graph (*CFG*) representation of the original code region is also given.<sup>2</sup> As output, this algorithm produces, for each of the resulting threads, a new CFG containing its corresponding instructions and the necessary communication instructions.

The thread model assumed here is that the program executes sequentially until it reaches a region that has been scheduled on multiple threads. Upon reaching such parallelized region, auxiliary threads are spawned, and each of them will execute one of the CFGs produced by MTCG. In this model, auxiliary threads do not spawn more threads. The main thread (which may also execute one of the new CFGs) then waits for completion of all the auxiliary threads. Once all auxiliary threads terminate, sequential execution resumes. This thread model is known as *fork-join*. In practice, the cost of spawning and terminating threads can actually be reduced by creating the threads only once, at the start of the program. The threads then execute a loop that continuously waits on the address of the code to be executed and invokes the corresponding code, until they are signaled to terminate. In this model, the work is statically assigned to threads. This is in contrast to dynamic scheduling [90].

Before going into the details in Algorithm 1, let us introduce the notation used.  $T_i$  denotes a block (thread) in  $\mathcal{P}$ , and  $CFG_i$  denotes its corresponding control-flow graph. For a given instruction I, bb(I) is the basic block containing I in the (original) CFG, and  $point_i(I)$  is the point in  $CFG_j$  corresponding to the location of I in CFG.

<sup>&</sup>lt;sup>2</sup>There are well-known algorithms to construct a CFG from a PDG derived from a sequential program [28, 100].

### Algorithm 1 MTCG

**Require:** *CFG*, *PDG*,  $\mathcal{P} = \{T_1, \ldots, T_n\}$ 1: for each  $T_i \in \mathcal{P}$  do // 1. create  $CFG_i$ 's basic blocks  $V_{CFG_i} \leftarrow create\_relevant\_basic\_blocks(CFG, PDG, T_i)$ 2: 3: end for 4: for each instruction  $I \in V_{PDG}$  do // 2. put instruction in its thread's CFG 5: let  $i \mid I \in T_i$  $add\_after(CFG_i, point_i(I), I)$ 6: 7: end for 8:  $COMM \leftarrow \emptyset$ 9: for each arc  $(I \rightarrow J) \in PDG$  [incl. transitive control dependences] do // 3. insert communication let  $T_i, T_j$  be such that  $I \in T_i$  and  $J \in T_j$ 10: if  $(T_i = T_i) \lor ((I, T_i) \in COMM)$  then 11: 12: continue 13: end if 14:  $COMM \leftarrow COMM \cup \{(I, T_i)\}$ 15:  $q \leftarrow get\_free\_queue()$ if  $dependence_type(I \rightarrow J) = Register$  then 16: // register dependences 17:  $r_k \leftarrow dependent\_register(I \rightarrow J)$  $add\_after(CFG_i, I, "produce [q] = r_k")$ 18: 19:  $add_after(CFG_i, I, "consume r_k = [q]")$ 20: else if  $dependence\_type(I \rightarrow J) = Memory$  then *II memory dependences* 21: add\_after(CFG<sub>i</sub>, I, "produce.rel [q]") add\_after(CFG<sub>i</sub>, I, "consume.acq [q]") 22: 23: *II control dependences* else 24:  $r_k \leftarrow register_operand(I)$ 25:  $add\_before(CFG_i, I, "produce [q] = r_k")$  $add\_before(CFG_i, I, "consume r_k = [q]")$ 26: 27:  $add_after(CFG_i, I, duplicate(I))$ 28: end if 29: end for 30: for each  $T_i \in \mathcal{P}$  do for each live-in register r in  $T_i$  do // initial communication 31: 32:  $q \leftarrow qet_free_queue()$ 33: add\_last(START, "produce [q] = r")  $add\_last(START_i, "consume r = [q]")$ 34: 35: end for 36: for each live-out register r defined in  $T_i$  reaching END do *II final communication* 37:  $q \leftarrow get_free_queue()$ 38:  $add\_last(END_i, "produce [q] = r")$  $add\_last(END, "consume r = [q]")$ 39: 40: end for 41:  $q \leftarrow get_free_queue()$ add\_last(END<sub>i</sub>, "produce.rel [q]") 42: 43: add\_last(END, "consume.acg[q]") 44: end for 45: for each  $T_i \in \mathcal{P}$  do // 4. create  $CFG_i$ 's arcs 46: for each branch instruction  $I \in T_i$  do 47:  $redirect\_target(I, closest\_relevant\_postdom_i(target(I)))$ 48: end for 49: for each  $B \in V_{CFG_i}$  do 50:  $CRS \leftarrow closest\_relevant\_postdom_i(succ(orig\_bb(B)))$ 51: add\_last(B, "jump CRS") 52: end for 53: end for

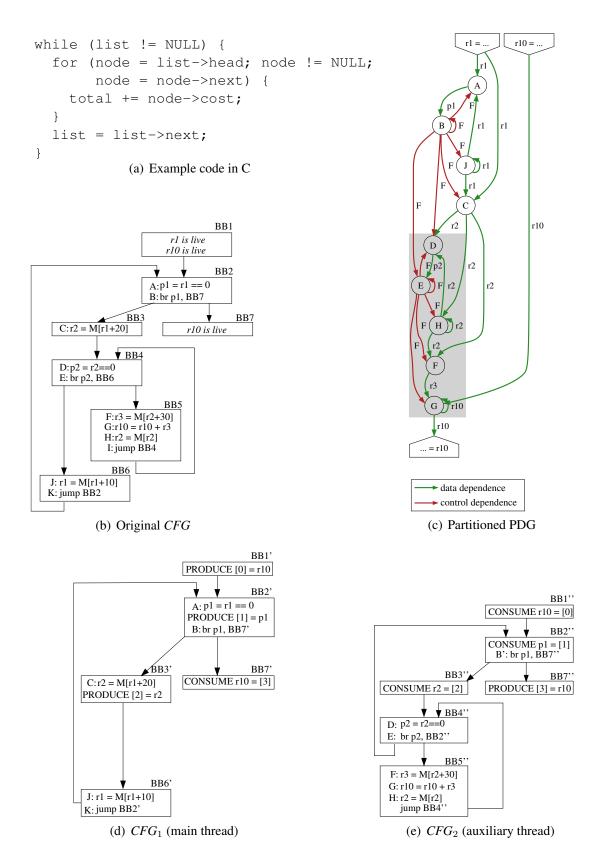

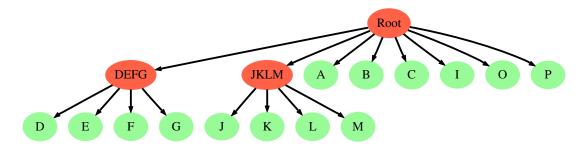

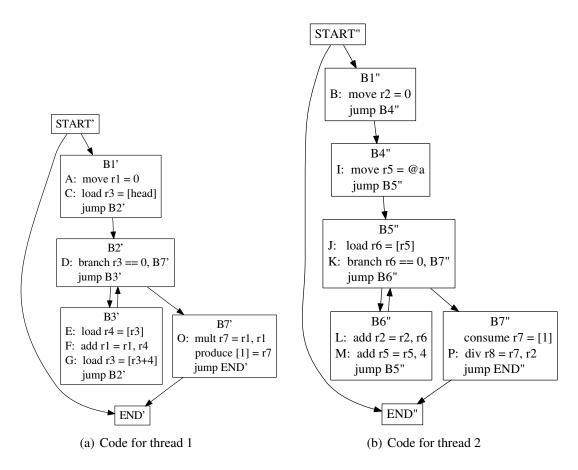

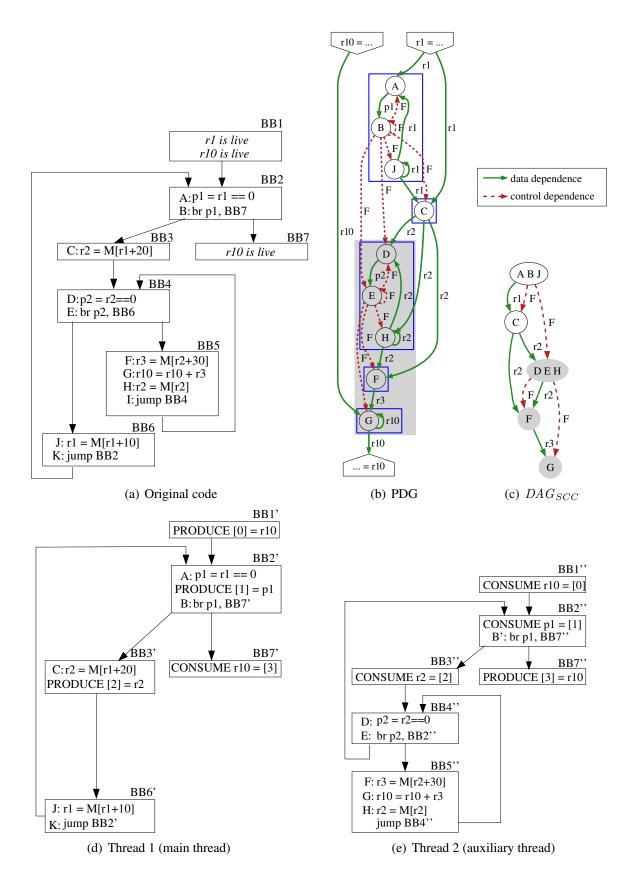

Figure 3.1: Example of the MTCG algorithm. (a) C source code; (b) original low-level code; (c) partitioned PDG; and (d)-(e) resulting multi-threaded code.

In essence, the MTCG algorithm has four main steps. Each of the following subsections describes one of these steps. As we describe these steps, we illustrate them on the example in Figure 3.1. Figure 3.1(a) contains the source code in C, and Figure 3.1(b) contains the corresponding code in a low-level IR. We illustrate how MTCG generates code for the partitioned PDG in Figure 3.1(c), where the nodes in the shaded rectangle are assigned to one thread, and the remaining instructions to another. In the PDG, data dependence arcs are annotated with the corresponding register holding the value, while control dependence arcs are labeled with the corresponding branch condition. In this example, there are no memory dependences. Special nodes are included in the top (bottom) of the graph to represent live-in (live-out) registers. The resulting code for the two threads is illustrated in Figures 3.1(d) and (e). In this example, the main thread also executes the code for one of the generated threads ( $CFG_1$ ).

## 3.1.1 Creating New CFGs' Basic Blocks

MTCG creates a new CFG ( $CFG_i$ ) for each thread  $T_i$ . Each  $CFG_i$  contains a basic block for each *relevant basic block* to  $T_i$  in the original CFG. The notion of relevant basic block is defined below. In its last step, described in Section 3.1.4, MTCG adds the arcs connecting the basic blocks in each  $CFG_i$ . These arcs are inserted in a way that guarantees the equivalence between the condition of execution of each new basic block and its corresponding block in the original CFG (see proof in Section 3.2).

**Definition 2** (Relevant Basic Block). A basic block B is relevant to a thread  $T_i$  if B contains either:

- 1. an instruction scheduled to  $T_i$ ; or

- 2. an instruction on which any of  $T_i$ 's instructions depends (i.e. a source of a dependence with an instruction in  $T_i$  as the target); or

- 3. a branch instruction that controls a relevant basic block to  $T_i$ .

The reason for including basic blocks containing instructions in  $T_i$  is obvious, as they will hold these instructions in the generated code. The reason for adding the basic blocks containing instructions on which  $T_i$ 's instructions depend is related to where communication instructions are inserted by MTCG, as described shortly. The third rule in Definition 2 is recursive, and it is necessary to implement the correct condition of execution of the basic blocks. This rule is related to how inter-thread control dependences are implemented by MTCG, as described Section 3.1.3.

Consider the example in Figure 3.1. For thread  $T_1 = \{A, B, C, J\}$ , besides the start block BB1 and the end block BB7, the only relevant basic blocks are BB2, BB3, and BB6. All these blocks are relevant to  $T_1$  by rule 1 in Definition 2, since there is no incoming dependence into this thread. For thread  $T_2 = \{D, E, F, G, H\}$ , besides the start and end blocks, several other basic blocks are relevant for different reasons. BB4 and BB5 contain instructions in  $T_2$ , and therefore are relevant by rule 1. Because of the dependences from  $T_1$ to  $T_2$ , with source instructions B and C (Figure 3.1(c)), the basic blocks that contain these instructions (BB2 and BB3) are relevant to  $T_2$  by rule 2. Again, no basic block is relevant due to rule 3 in this case.

#### **3.1.2** Moving Instructions to New CFGs

The second step of MTCG (lines 4 to 7) is to insert the instructions in  $T_i$  into their corresponding basic blocks in  $CFG_i$ . MTCG inserts the instructions in the same relative order as in the original code, so that intra-thread dependences are naturally respected.

Figures 3.1(d) and (e) illustrate the instructions inserted in their threads, in the basic blocks corresponding to the instructions' original basic blocks.

## 3.1.3 Inserting Inter-Thread Communication

The third step of the algorithm (lines 8 to 44) is to insert communication primitives to implement each inter-thread dependence. We represent communication primitives by produce and consume instructions [84]. The produce and consume instructions are inserted in pairs, so that, statically, each produce feeds one consume, and each consume is fed by one produce. For each inter-thread dependence, a separate communication queue is used. Although a single queue is sufficient, multiple queues are used to maximize the freedom of subsequent single-threaded scheduling. Furthermore, a queue-allocation technique can later reduce the number of queues necessary, analogously to register allocation.

Depending on where the communication primitives are inserted with respect to the parallel region, they can be of three types: *intra-region* (i.e. inside the parallelized region), *initial*, or *final* communications. We first describe the insertion of the most interesting ones, the intra-region communications, followed by the initial and final communications.

#### **Intra-Region Communications**

In order to preserve the conditions under which each dependence occurs, MTCG adopts the following strategy.

**Property 1** (Basic Communication Placement). *Each intra-region dependence is communicated at the program point of its source instruction.*

This strategy is simple to implement, and it also simplifies the proof of correctness of the algorithm (Section 3.2). However, this strategy can result in a suboptimal number of inter-thread communications. Better algorithms to place communication primitives are described in Chapter 4.

In Algorithm 1,  $add\_before(CFG_i, I, instr)$  inserts instr in  $CFG_i$  at the point right before instruction I's position in the original CFG, and  $add\_after$  works analogously. The  $add\_last(B, I)$  function inserts instruction I as the last instruction in basic block B.

The actual communication instructions inserted depend on the type of the dependence, as illustrated in Algorithm 1:

• Register Dependences: These are implemented by communicating the register in question.

- Memory Dependences: For these, purely synchronization primitives are inserted to enforce that their relative order of execution is preserved. This is dependent on the target processor's memory consistency model. In this work, we assume Itanium 2's memory consistency model. In Algorithm 1, synchronization primitives are represented by produce.rel and consume.acq instructions, which implement the release and acquire semantics in the memory system.<sup>3</sup>

- Control Dependences: In the source thread, before the branch is executed, its register operands are sent. In the target thread, consume instructions are inserted to get the corresponding register values, and then an equivalent branch instruction is inserted to mimic the same control behavior. For simplicity, Algorithm 1 assumes that branches have a single register operand.

The call-exit control dependences discussed in Section 2.2 require a different code generation strategy, which is not illustrated in Algorithm 1. For these control dependences, a consume instruction from a special queue is inserted in the target thread at the point corresponding to the call-site. We name the value consumed from this special queue the *terminate* value. After the consume of this *terminate* value, a branch is inserted to check this value and to jump to terminating code if the value is *true*. In the source thread, a produce *false* into this special queue is inserted after the function call. This signals the target thread to continue execution in case the function returns normally. Additionally, in the source thread, a produce *true* is inserted in a handler installed to executed upon program termination. This causes the target thread to terminate as well.

In the example from Figure 3.1, there are two inter-thread, intra-region dependences. First, instruction C in  $T_1$  writes into register r2 that is used by instructions D, F, and H

<sup>&</sup>lt;sup>3</sup>In other words, produce.rel is guaranteed to execute only after all previous memory instructions commit. Analogously, consume.acq is guaranteed to commit before all successive memory instructions are executed.

in  $T_2$ . This register data dependence is communicated through queue 2. The produce and consume instructions are inserted right after the points corresponding to instruction C in BB3. The other inter-thread dependence is a control dependence from branch B in  $T_1$ , which controls instructions in  $T_2$ . This dependence is satisfied through queue 1. In  $T_1$ , the register operand (p1) is sent immediately before instruction B. In  $T_2$ , the value of p1 is consumed and a copy of branch B(B') is executed.

As mentioned in line 9 of Algorithm 1, the MTCG algorithm also needs to communicate *transitive control dependences* in the PDG in order to implement the relevant blocks for a thread. This is related to rule 3 in Definition 2. The reason for this is control dependences' implementation, which consumes the branch operands and duplicates the branch in the target thread. In order to enforce the correct conditions of execution of these instructions in the target thread (i.e. to create the relevant basic blocks to contain these instructions), it is necessary to communicate the branches controlling the blocks where these instructions are inserted. This reasoning follows recursively, thus resulting in the necessity of communicating the transitive control dependences.

#### **Initial Communications**

Communication primitives may need to be inserted for register values that are live at the entry of the parallelized region, similarly to OpenMP's firstpriviate [71]. More specifically, if a register definition from outside the parallelized region reaches a use in an instruction assigned to thread  $T_i$ , then the value of this register has to be communicated from the main thread to  $T_i$ .<sup>4</sup> These communication primitives are inserted at the *START* basic block in *CFG* and at its corresponding *START*<sub>i</sub> basic block in *CFG*<sub>i</sub>. This step is illustrated in lines 31-35 in Algorithm 1.

In the example from Figure 3.1, the main thread executes the code for  $T_1$ , so no initial communication is necessary for  $T_1$ . For  $T_2$ , instruction G uses the value of r10 defined

<sup>&</sup>lt;sup>4</sup>The exception is in case  $T_i$  is run on the main thread.

outside the parallelized region, and therefore this register needs to be communicated. This dependence is communicated through queue 0, and the produce and consume instructions are inserted in BB1, the *START* basic block.

Since auxiliary threads are spawned at the entry of the parallelized region<sup>5</sup>, no initial communication for memory and control dependences are necessary. In other words, auxiliary threads are only spawned when the execution reaches the parallelized region, and any memory instruction before this region will have already executed.

#### **Final Communications**

At the end of the parallelized region, the auxiliary threads may have to communicate back to the main thread, which is similar to OpenMP's lastprivate [71]. Final communications may be necessary not only for register values, but also for memory. We discuss these two cases below.

For every register r defined by an instruction assigned to thread  $T_i$ , r needs to be sent to the main thread if two conditions hold. First, r must be live at the end of the parallelized region (*END*). Second, a definition of r in  $T_i$  must reach *END*. Lines 36-40 in Algorithm 1 handle this case.

In Figure 3.1, it is necessary to communicate the value of register r10 from  $T_2$  to the main thread at the end of the parallelized region. This communication uses queue 3, and the produce and consume instructions are inserted in the *END* blocks (corresponding to BB7).

A problem arises in case multiple threads have definitions of r that reach the exit of the parallelized region. Depending on the flow of control, a different thread will have the correct/latest value of r, which needs to be communicated back to the main thread. To address this problem, two solutions are possible. One alternative is to associate a time-stamp for r in each thread, so that it is possible to tell which thread wrote r last. In this scheme, at the

<sup>&</sup>lt;sup>5</sup>At least conceptually; see discussion earlier in Section 3.1.