# Modes, Registers and Addressing and Arithmetic Instructions

CS 217

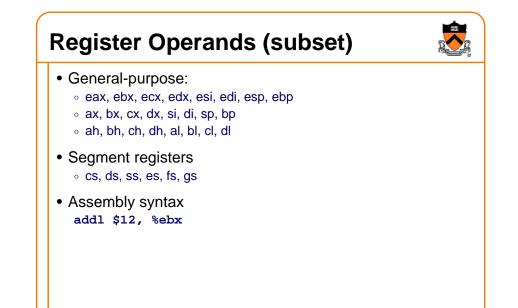

# **Revisit IA32 General Registers**

- 8 32-bit general-purpose registers (e.g. EAX)

- Each lower-half can be addressed as a 16-bit register (e.g. AX)

- Each 16-bit register can be addressed as two 8-bit registers (e.g AH and HL)

| 1 1 | 6 15 | 8  | 7  | 0 |   |

|-----|------|----|----|---|---|

|     | A    | Η  | AL |   | ł |

|     | E    | sн | BL |   | E |

|     | C    | н  | CL |   | ( |

|     | C    | н  | DL |   | 0 |

|     |      | 5  | SI |   |   |

|     |      | 0  | DI |   |   |

|     |      | E  | βP |   |   |

|     | SP   |    |    |   |   |

|     |      |    |    |   |   |

3

AX EAX: Accumulator for operands, results

BX EBX: Pointer to data in the DS segment.

CX ECX: Counter for string, loop operations. DX EDX: I/O pointer.

> ESI: Pointer to DS data, string source EDI: Pointer to ES data, string destination EBP: Pointer to data on the stack ESP: Stack pointer (in the SS segment)

# **EIP Register**

- Instruction Pointer or "Program Counter"

- Software change it by using

- Unconditional jump

- Conditional jump

- Procedure call

- Return

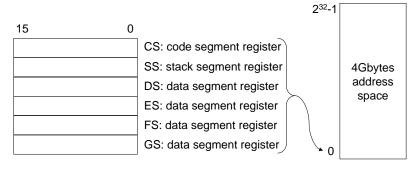

# **Segment Registers**

- · IA32 memory is divided into segments, pointed by segment registers

- Modern operating system and applications use the (unsegmented) memory mode: all the segment registers are loaded with the same segment selector so that all memory references a program makes are to a single linear-address space.

# **EFLAG Register**

| Reserved (set to 0)       I       V       I       V       I       V       I       V       I       V       I       V       I       V       I       V       I       V       I       V       I       V       I       V       I       V       I       V       I       V       I       V       I       V       I       V       I       V       I       V       I       V       I       V       I       V       I       V       I       V       I       V       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I | 31                                                                                                                                                                                                                                                                                       | 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1                                 | 0      |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|--------|

| Virtual interrupt pending                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Reserved (set to 0)                                                                                                                                                                                                                                                                      | I V V A V R O T P F F F F F F O A O F 1<br>P P F C M F O T L F F F F F F F O F O F O F 1 | C<br>F |

| Carry flag                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Virtual interrupt pending -<br>Virtual interrupt flag<br>Alignment check<br>Virtual 8086 mode<br>Resume flag<br>Nested task flag<br>I/O privilege level<br>Overflow flag<br>Direction flag<br>Interrupt enable flag<br>Trap flag<br>Sign flag<br>Zero flag<br>Auxiliary carry flag or au |                                                                                          |        |

# **Other Registers**

- Floating Point Unit (FPU) (x87)

- Eight 80-bit registers (ST0, ..., ST7)

- 16-bit control, status, tag registers

- 11-bit opcode register

- 48-bit FPU instruction pointer, data pointer registers

- MMX

- Eight 64-bit registers

- SSE and SSE2

- Eight 128-bit registers

- 32-bit MXCRS register

- System

- I/O ports

- Control registers (CR0, ..., CR4)

- Memory management registers (GDTR, IDTR, LDTR)

- Debug registers (DR0, ..., DR7)

- Machine specific registers

- Machine check registers

- Performance monitor registers

# **Three Addressing Models**

### Flat model

- The modern way of memory addressing

- All segment registers are loaded with 0

### Segmented model

- · Segment registers are loaded differently

- The goal is to increase protection

- Real-addressing model

- Backward compatible with 8086

- Each segment is 64Kbytes

- Segments are laid out in 20-bit address space

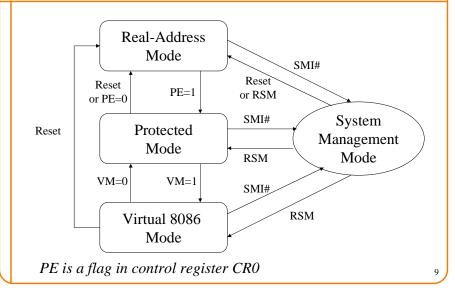

# **Four Operating Modes**

### Real-address mode

- Let the processor address 1Mbytes of "real" memory (20-bit address).

- Also called "unprotected" mode since operating system (such as DOS) code runs in the same mode as the user applications.

- How: Power-up or a reset

- Why: Backward compatible with early Intel processors such as 8086

- Switch to protected mode: a single instruction

### · Protected mode

- Let the processor address 4GBytes of virtual memory (32-bit address) and will extend to 64-bit this year

- Preferred mode for a modern operating system

- Use virtual memory and provide protections.

- · System management mode

- For fast state snapshot and resumption (power management)

- Virtual-8086 mode

- Allow the processor to execute 8086 code software in the protected, multitasking environment

# **IA32 Operating Mode Transition**

# Instruction Opcode What to do Source operands Immediate (in the instruction itself) Register Memory location I/O port Destination operand Register Memory location I/O port Assembly syntax Opcode source1, [source2,] destination

# **Types of Instructions**

- · Data transfer: move from source to destinatio

- Arithmetic: arithmetic on integer

- Floating point: x87 FPU move, arithmetic

- Logic: bitwise logic operations

- · Control transfer: conditional and unconditional jumps, procedure calls

- String: move, compare, input and output

- Flag control: Control fields in EFLAGS

- Segment register: Load far pointers for segment registers

- SIMD

- MMX: integer SIMD instructions

- SSE: 32-bit and 64-bit floating point SIMD instructions

- SSE2: 128-bit integer and float point SIMD instructions

- System

- Load special registers and set control registers (including halt)

Data Transfer Instructions

12

10

- •mov{b,w,l} source, dest

- General move instruction

- •push{w,l} source

| pushl | %ebx | # | equivalent | inst | ruct | ions   |

|-------|------|---|------------|------|------|--------|

|       |      |   | S          | subl | \$4, | %esp   |

|       |      |   | r          | novl | %ebx | (%esp) |

•pop{w,1} dest

```

popl %ebx # equivalent instructions

movl (%esp), %ebx

dill dia

```

- addl \$4, %esp

- Many more in Intel manual (volume 2)

- Type conversion, conditional move, exchange, compare and exchange, I/O port, string move, etc.

# **Immediate Operands**

- All arithmetic instructions allow immediate as source operands

- Example in gcc assembly

movl \$10, %eax # move 10 to EAX registe

14

# **Memory Operands**

13

- Addressing memory

- 8-bit is the smallest unit

- 32-bit addresses (protected mode, will be extended to 64-bit later)

31

IA32 is little endian

### Examples

movw \$5, %ax

$\begin{bmatrix} A \\ 7 & 0 \end{bmatrix}$  byte  $\begin{bmatrix} A+1 & A \\ 15 \end{bmatrix}$  16-bit word  $\begin{bmatrix} A+3 & A+2 & A+1 & A \end{bmatrix}$  32-bit word

# **Bitwise Logic Instructions**

### Simple instructions

and{b,w,l} source, dest dest = source & dest or{b,w,l} source, dest dest = source | dest xor{b,w,l} source, dest dest = source ^ dest not{b,w,l} dest dest = ^dest sal{b,w,l} source, dest (arithmetic) dest = dest << source sar{b,w,l} source, dest (arithmetic) dest = dest >> source

- Many more in Intel Manual (volume 2)

- Logic shift

- rotation shift

- Bit scan

- Bit test

- Byte set on conditions

# **Number Systems**

17

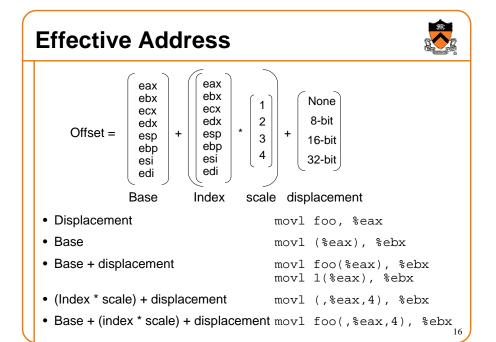

• General form of a number in base b is

$$x = x_n b^n + x_{n-1} b^{n-1} + \dots + x_1 b^1 + x_0 b^0 + x_{-1} b^{-1} + \dots + x_{-m} b^{-m}$$

where x<sub>i</sub> are the **positional coefficients**

Modern computers use binary arithmetic, i.e., base 2

$$140_{10} = 1 \times 10^{2} + 4 \times 10^{1} + 0 \times 10^{0}$$

= 1 \times 2^{7} + 0 \times 2^{6} + 0 \times 2^{5} + 0 \times 2^{4} + 1 \times 2^{3} + 1 \times 2^{2} + 0 \times 2^{1} + 0 \times 2^{0}

= 10001100<sub>2</sub>

= 2 \times 8^{2} + 1 \times 8^{1} + 4 \times 8^{0} = 214<sub>8</sub>

= 8 \times 16^{1} + C \times 16^{0} = 8C\_{16}

### Simple instructions

- add{b,w,l} source, dest dest = source + dest sub{b,w,l} source, dest dest = dest - sourceinc(b,w,l) dest dest = dest + 1 dec{b,w,l} dest dest = dest - 1 neg(b,w,l) dest dest = ^dest cmp{b,w,l} source1, source2 source2 - source1 • Multiply • mul (unsigned) or imul (signed) mull %ebx # edx, eax = eax \* ebx • Divide • div (unsigned) or idiv (signed) idiv %ebx # edx = edx,eax / ebx

- Many more in Intel manual (volume 2) • adc, sbb, decimal arithmetic instructions

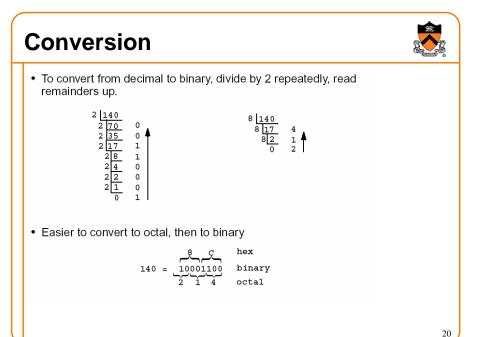

# Addition

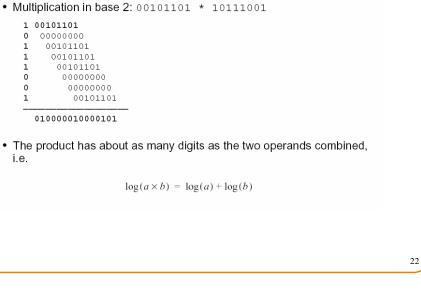

# Multiplication

# **Machine Arithmetic**

21

- Computers usually have a fixed number of binary digits ("bits"), e.g., 32

bits

- For example, using 6 bits, numbered 0 to 5 from the right

```

largest number 111111_2 = 63_{10} = 2^6 - 1

smallest number 00000_2 = 0

```

• What is 50 + 20?

```

110010

+ 010100

_____

1000110

```

- The highest bit doesn't fit, so we get  $000110_2 = 6_{10}$

- Spilling over the lefthand side is overflow

# Signed Magnitude

### <u>Sign-magnitude</u> notation:

- bit n-1 is the sign; 0 for +, 1 for -

- bits n-2 through 0 hold an unsigned number

- largest number  $011111_2 = 31_{10} = 2^{6-1} 1$

smallest number  $111111_2 = -31_{10} = -(2^{6-1} - 1)$

- · Addition and subtraction are complicated when signs differ

- Sign-magnitude is rarely used

# **One's Complement**

- <u>One's-complement</u> notation:  $-k = (2^n 1) k = 11111...(n \text{ bits}) k$ bit n - 1 is the sign; bits n - 2 through 0 hold an unsigned number bits n - 2 through 0 hold <u>complement</u> of negative numbers largest number  $011111_2 = 31_{10} = 2^{6-1} - 1$ smallest number  $100000_2 = -31_{10} = -(2^{6-1} - 1)$

- Addition and subtraction are easy, but there are **2** representations for 0

```

a-b=a+(r^n-1-b)+1

```

```

a - b = a + b_{1C} + 1

```

# **Two's Complement**

• <u>Two's-complement</u> notation:  $-k = 2^n - k = (2^n - 1) - k + 1$ bit n - 1 is the sign; bits n - 2 through 0 hold an unsigned number bits n - 2 through 0 hold the <u>complement</u> of a negative number <u>plus 1</u> largest number 011111<sub>2</sub> = 31<sub>10</sub> = 2<sup>6-1</sup> - 1

smallest number  $100000_2 = -32_{10} = -2^{6-1}$ ; note **asymmetry**

• To negate a 2's compl. number: first complement all the bits, then add 1

|     | start with | complement | increment |     |

|-----|------------|------------|-----------|-----|

| +6  | 000110     | 111001     | 111010    | - 6 |

| - 6 | 111010     | 000101     | 000110    | +6  |

| +0  | 000000     | 111111     | 000000    | - 0 |

| +1  | 000001     | 111110     | 111111    | -1  |

| +31 | 011111     | 100000     | 100001    | -31 |

| -31 | 100001     | 011110     | 011111    | +31 |

| -32 | 100000     | 011111     | 100000    | -32 |

|     |            |            |           |     |

26

28

$-k_{2C} = k+1$

# **Two's Complement (cont)**

25

|                         |                           |            |                          | -                                  |            |      | -                        | -          |                           |               |

|-------------------------|---------------------------|------------|--------------------------|------------------------------------|------------|------|--------------------------|------------|---------------------------|---------------|

| • Ad                    | ding 2                    | 's-0       | complem                  | ent nur                            | nbers      | : ig | nore sigr                | ns, add    | unsigned bit strings      |               |

| +                       | +20                       | +          | 010100<br>111001         | 4                                  | -20<br>+ 7 | +    | 101100<br>000111         |            | $a-b=a+(r^n-1-$           | - <i>b</i> )+ |

|                         | +13                       |            | 001101                   |                                    | -13        |      | 110011                   |            | $a-b=a+b_{2C}$            |               |

| +                       |                           |            | 010100<br>000111         | +                                  | -20<br>- 7 | +    | 101100<br>111001         |            |                           |               |

|                         | +27                       |            | 011011                   |                                    | -27        |      | 100101                   |            |                           |               |

| <ul> <li>Sig</li> </ul> | ned o                     | ver        | flow occ                 | urs if                             |            |      |                          |            |                           |               |

| tl                      | ne carry                  | <u>int</u> | <u>o</u> the sign        | bit differs                        | from t     | ne c | arry <u>out</u> of       | f the sign | bit                       |               |

| +                       | +20+17                    | +          | 010100<br><u>0</u> 10001 | +                                  | -20        | +    | 101100<br><u>1</u> 01111 |            |                           |               |

|                         | -27                       |            | 100101                   |                                    | +27        |      | 011011                   |            |                           |               |

| c                       | me ha<br>overflow<br>arry |            | signed                   | both UN:<br>overflow<br>ed overflo | 0          | l ar | nd signed                | d, but fla | ags <u>two</u> conditions |               |

|                         |                           |            |                          |                                    |            |      |                          |            |                           |               |

# **Sign Extension**

• To convert from a small signed integer to a larger one, copy the sign bit

|        | +5       | -5           |

|--------|----------|--------------|

| 4 bits | 0101     | <u>1</u> 011 |

| 8 bits | 00000101 | 11111011     |

|        |          |              |

• To convert a large signed integer to a smaller one: check trunced bits

| 8 bits<br>4 bits | +5<br>00000101<br>0101          | -5<br>11111011<br>1011          | OK!  |

|------------------|---------------------------------|---------------------------------|------|

| 8 bits<br>4 bits | +20<br><u>0001</u> 0100<br>0100 | -20<br><u>1110</u> 1100<br>1100 | Bad! |

• Hardware does extension, but may not check for truncation; nor does C

```

short small = -50; long big = small;

printf("%d %d\n, small, big); -50 -50

long big = 40000; short small = big;

printf("%d %d\n", small, big); -25536 40000

char c = 255;

printf("%d\n", c); -1

```

# Summary

- IA32 is a complex machine

- $\circ\,$  Three memory models: flat, segmented, real-address

- $\circ\,$  Four operating modes: real, protected, system mgmt, virtual 8086

- $\circ~$  Many kinds of instructions

- Things to remember

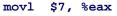

- Five types of memory operands (immediate, base, base+displacement, index\*scale + displacement, base+index\*scale+displacement

- Two's complement