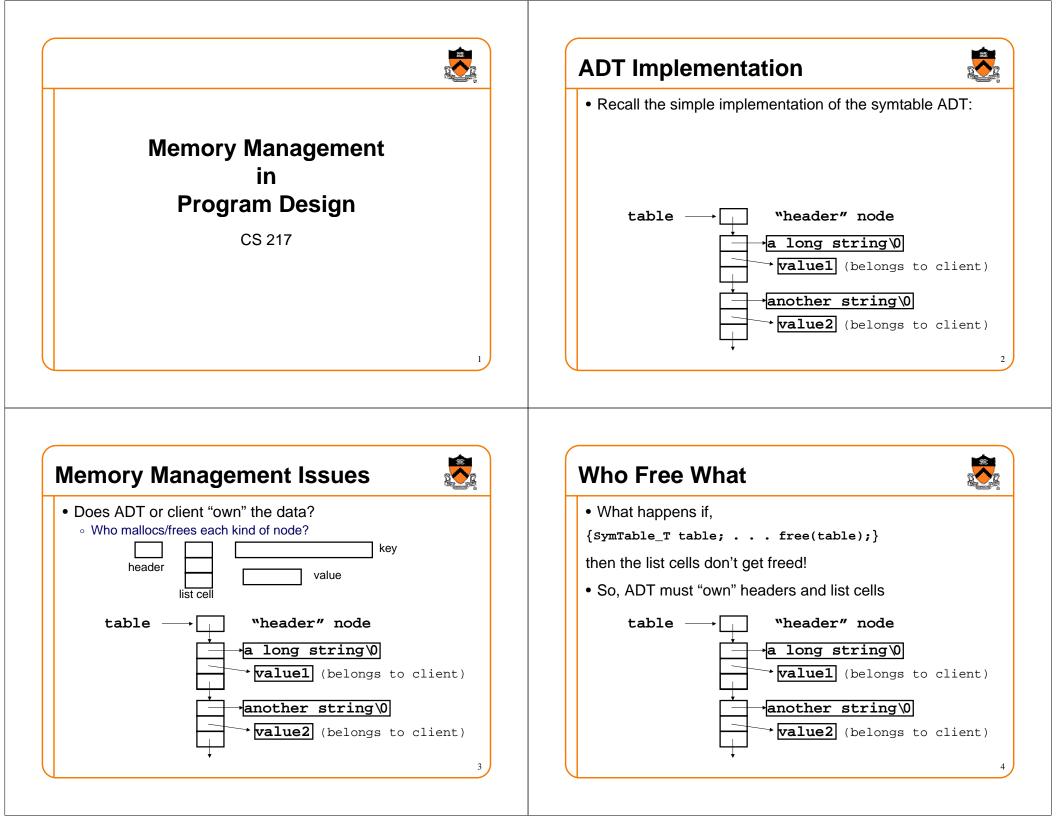

## Who Free What, cont'd

- ADT just sees void \*value;

- Value pointer might be root of big data structure, all the pieces need to be freed.

- Thus, client must "own" the value nodes.

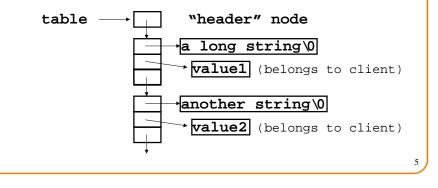

## Who Owns The Key?

- Both client and ADT "know" about char \*key;

- Therefore, we are faced with a design choice

- Choice 1: client owns the key.

- Consequence: must call SymTable\_put only with a string that will last a long time. (But our client didn't do that!)

#### **Previous Example Overwrites "line"**

```

int main(int argc, char *argv[]) {

char line[MAXLINE];

SymTable_T table = SymTable_new();

struct stats *v;

while (fgets(line, MAXLINE, stdin)) {

v = SymTable_get(table, line);

if (!v) {

v = makeStats(0);

SymTable_put(table, line, v);

}

SymTable_map(table, maybeprint, NULL);

return EXIT_SUCCESS;

}

```

# Choice 2: ADT owns the key

• Consequence: **SymTable\_put** must copy its **key** argument into a newly malloc'ed string object.

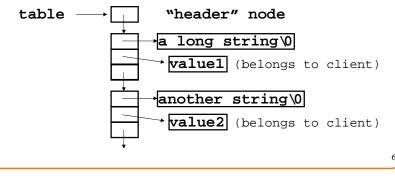

### Put Away Your Toys...

9

11

- When client is done with a symbol table, it should give the memory back.

- But client can't call free directly (as we already demonstrated)

- So there must be an interface function for client to say "I'm done with this"

- It should free the header, list cells, strings

SymTable\_free(SymTable\_T table);

- Should it free the values?

- Can't do it by calling free directly (as we already demonstrated)

- Another design choice!

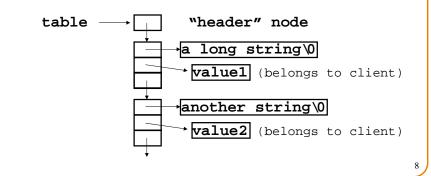

## **Options to Free Values**

- Option 1: Client frees all the values before calling SymTable\_free(table)

- Can do this using SymTable\_map(table, free\_it, NULL);

- $\circ\,$  Minor bother: temporarily leaves dangling pointers in the table

- $\circ~$  Minor bother: it's clumsy

- Option 2: SymTable\_free calls client function

- void SymTable\_free(SymTable\_T table,

void (\*f)(char \*key, void \*value, void \*extra), void \*extra);

10

- /\* Free entire table. During this process, if f is not NULL, apply f to each binding in table. It is a checked runtime error for table to be NULL. \*/

- We will choose Option 1.

CS 217

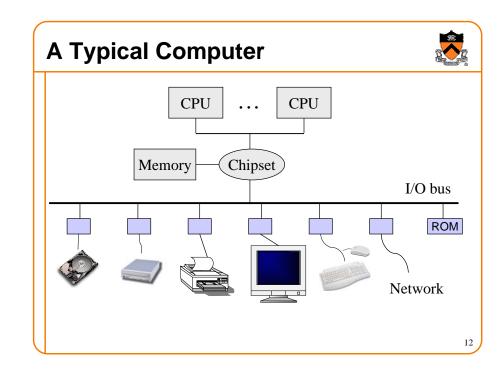

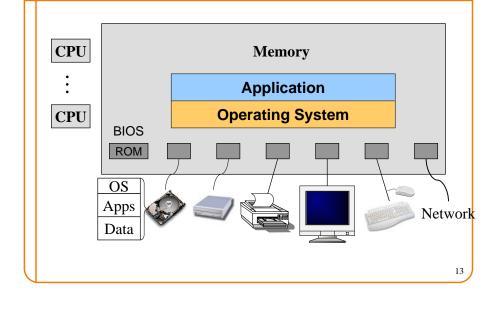

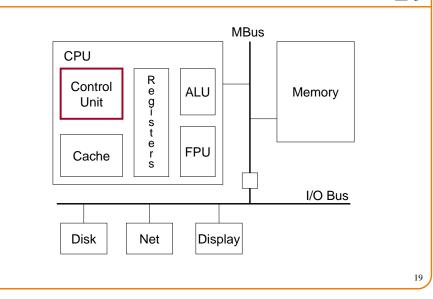

## **A Typical Computer System**

## **OS Service Examples**

- · Examples that are not provided at user level

- System calls: file open, close, read and write

- Control the CPU so that users won't stuck by running

while (1);

- Protection:

- Keep user programs from crashing OS

- Keep user programs from crashing each other

- Examples that can be provided at user level

- Read time of the day

- Protected user level stuff

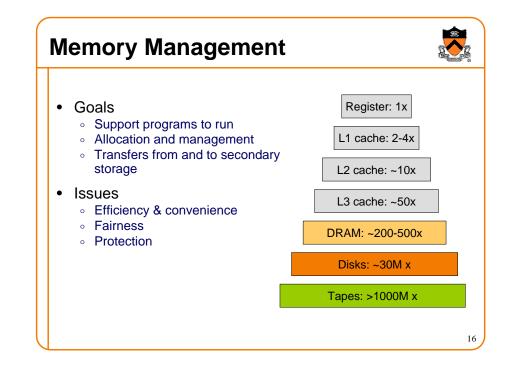

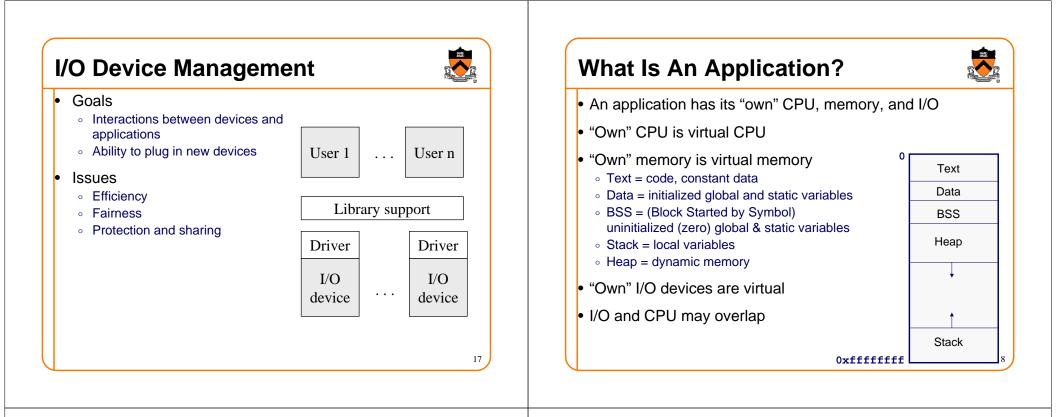

#### **Processor Management**

- Goals

- Overlap between I/O and computation

- Time sharing

- Multiple CPU allocations

- Issues

- Do not waste CPU resources

- Synchronization and mutual exclusion

- Fairness and deadlock free

15

14

## **General Computer Architecture**

#### **General Instruction Execution**

- CPU's control unit executes a program PC ← memory location of first instruction while (PC != last\_instr\_addr) execute(MEM[PC]);

- Multiple phases...

- Fetch: instruction fetch; increment PC

- Execute: arithmetic instructions, compute branch target address, compute memory addresses

- Memory access: read/write memory

- Store: write results to registers

| Fetch | Execute | Memory | Store | Fetch | Execute | Memory | Store |

|-------|---------|--------|-------|-------|---------|--------|-------|

|-------|---------|--------|-------|-------|---------|--------|-------|

# **Concept of Instruction Pipelining**

#### • A simple pipeline

| Fetch | Execute | Memory  | Store   |        |       |

|-------|---------|---------|---------|--------|-------|

|       | Fetch   | Execute | Memory  | Store  |       |

|       |         | Fetch   | Execute | Memory | Store |

- What about branch instruction? •

- Modern CPUs usually have deep pipelines

- Pentium II has a 10-stage pipeline

- Pentium 4 has a 20-stage pipeline

- $\,\circ\,$  They all have sophisticated branch prediction mechanisms

#### Instructions

- High-level language x = a + b;

- Assembly language movl 12(%ebp), %eax addl 8(%ebp), %eax

- Machine code

000000110000110001000101

110010010000100001000101

- Symbolic Representation

- Bit-encoded Representation

## **Machine Code**

21

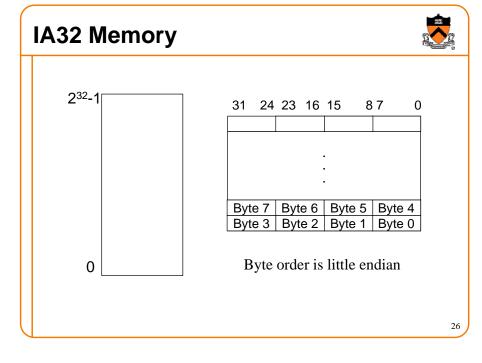

- IA32 has variable-sized instructions

- Example:

push %ebp

mov %esp,%ebp

0x8B 0xE589

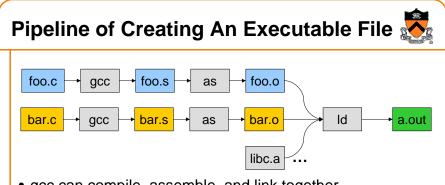

- gcc can compile, assemble, and link together

- Compiler part of gcc compiles a program into assembly

- Assembler compiles assembly code into relocatable object file

- Linker links object files into an executable

22

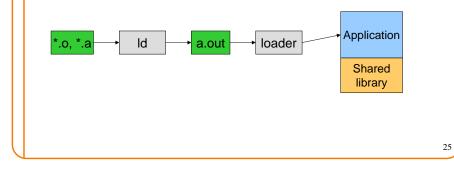

## **Execution (Run An Application)**

- On Unix, "loader" does the job

- Read an executable file

- Layout the code, data, heap and stack

- Dynamically link to shared libraries

- Prepare for the OS kernel to run the application

## **IA32 Architecture Registers**

| 31                                 | 15 8<br>AH<br>BH<br>CH<br>DH<br>S<br>C<br>C<br>C | AL<br>BL<br>CL<br>DL<br>P<br>SI | 16-bit<br>AX<br>BX<br>CX<br>DX | 32-bit<br>EAX<br>EBX<br>ECX<br>EDX<br>EBP<br>ESI<br>EDI<br>ESP | 15 ( | CS<br>DS<br>SS<br>ES<br>FS<br>GS<br>errs |  |  |

|------------------------------------|--------------------------------------------------|---------------------------------|--------------------------------|----------------------------------------------------------------|------|------------------------------------------|--|--|

| General-purpose registers          |                                                  |                                 |                                |                                                                |      |                                          |  |  |

| EFLAGS register                    |                                                  |                                 |                                |                                                                |      |                                          |  |  |

| EIP (Instruction Pointer register) |                                                  |                                 |                                |                                                                |      |                                          |  |  |

## **Upcoming Lectures ...**

- Mode, registers and addressing

- Arithmetic and logic Instructions

- Control transfer instructions

- Assembly directives

- Assembler