Finite State Machines (FSMs) and RAMs and inner workings of CPUs COS 116, Spring 2010 Guest: Szymon Rusinkiewicz

# Recap

- Combinational logic circuits: no cycles, hence no "memory"

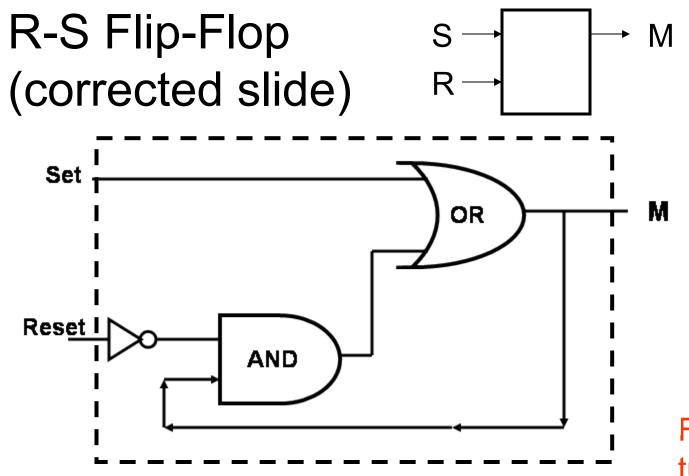

- Sequential circuits: cycles allowed; can have memory as well as "undefined"/ambiguous behavior

- Clocked sequential circuits: Contain D flip flops whose "Write" input is controlled by a clock signal

- M becomes 1 if Set is turned on

- M becomes 0 if Reset is turned on

- Otherwise (if both are 0), M just remembers its value

Forbidden to turn on both Set and Reset simultaneously (value is "ambiguous")

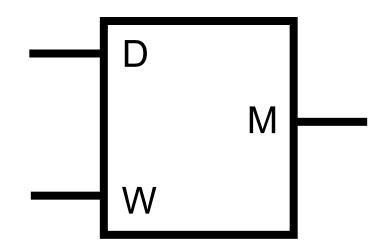

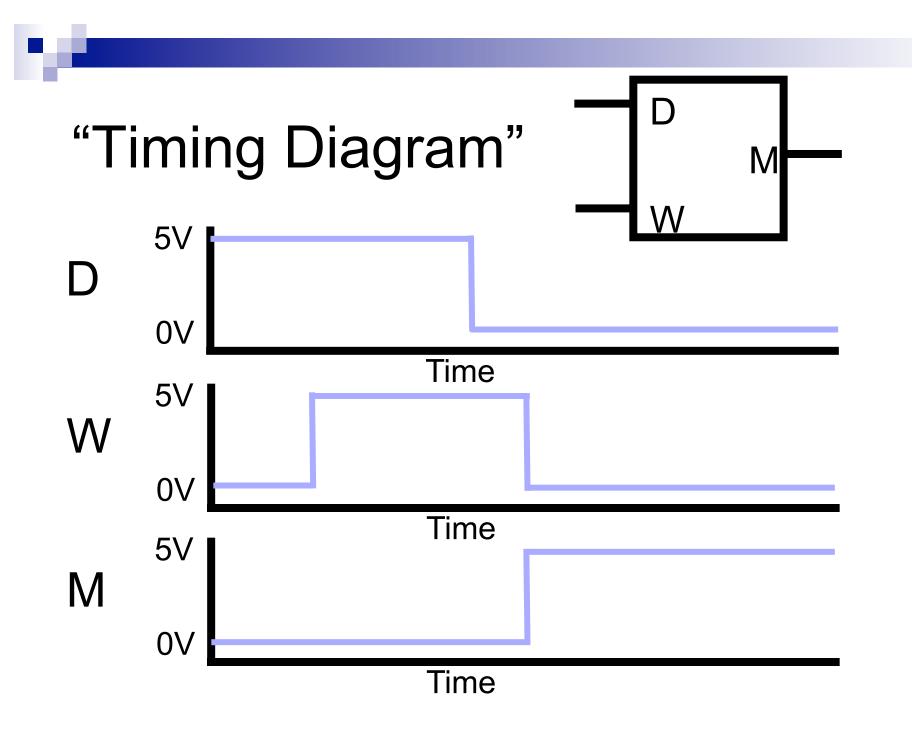

# Recap: D Flip Flop

Basic Memory Block – stores 1 bit.

If we "toggle" the write input (setting it 1 then setting it 0) then M acquires the value of D.

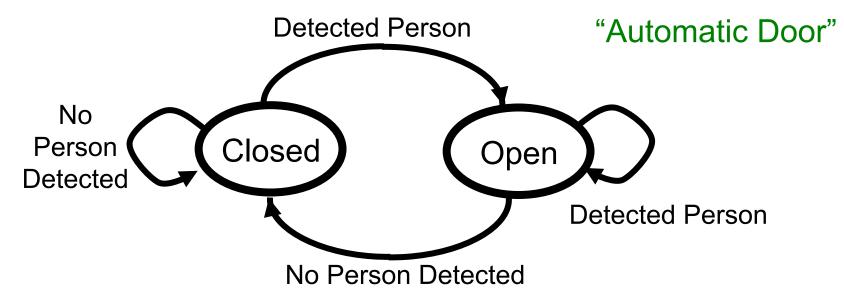

# Finite State Machines (FSMs)

- Finite number of states

- Machine can produce outputs, these depend upon current state only

- Machine can accept one or more bits of input; reading these causes transitions among states.

What are some examples of FSMs?

How can we implement a FSM using logic gates etc.?

- If number of states = 2<sup>k</sup> then represent "state" by k boolean variables.

- Identify number of input variables

- Write truth table expressing how "next state" is determined from "current state" and current values of the input.

- •Express as clocked synchronous circuit.

Example: 4-state machine; 1 bit of input; No output

State variables: P, Q Input variable: D

Next value of  $P = (P + Q) \cdot D$ Next value of Q = P

What is its state diagram?

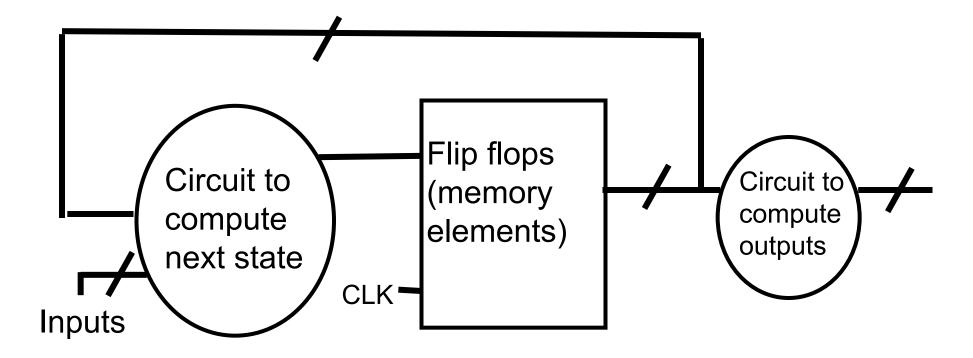

## **Implementation: General Schematic**

K Flip flops allow FSM to have 2<sup>K</sup> states

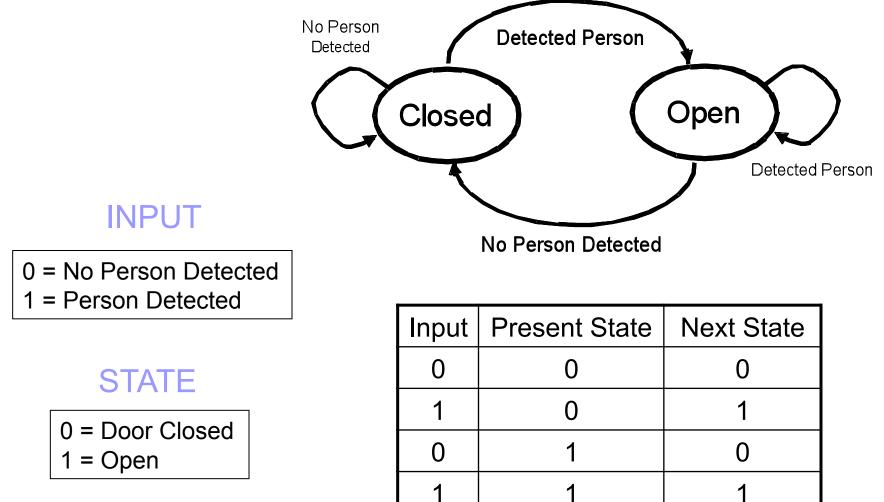

# Implementing door FSM as synchronous circuit

## Implementation of door FSM (contd)

## Next....

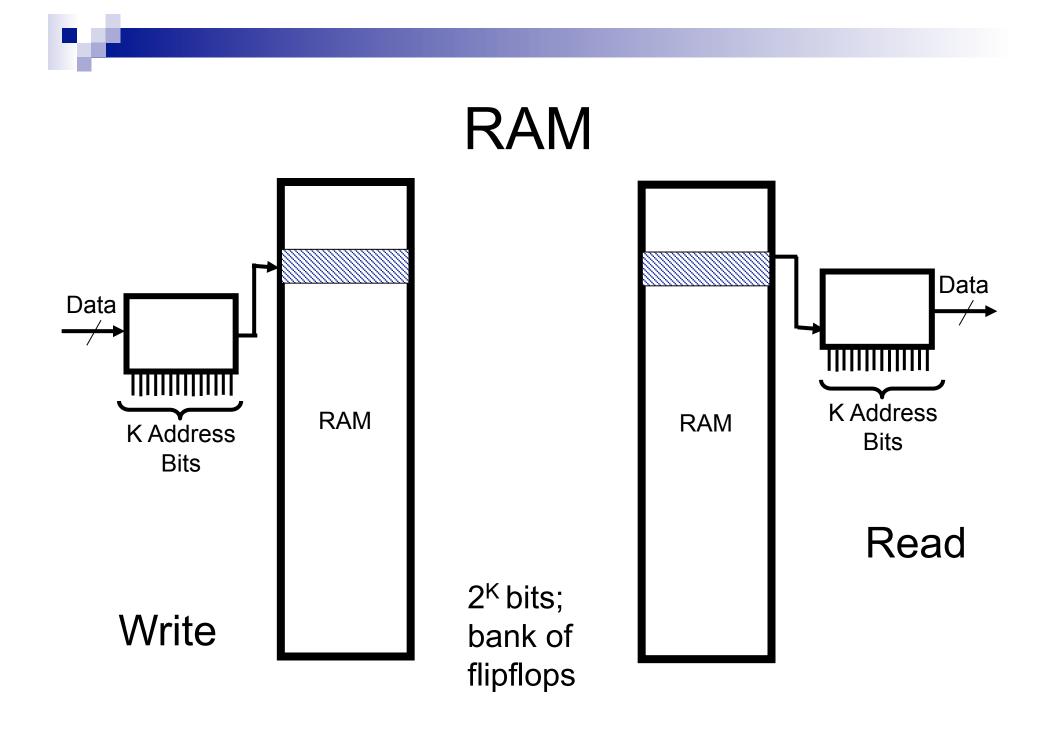

#### Random Access Memory (RAM)

#### Memory where each location has an address

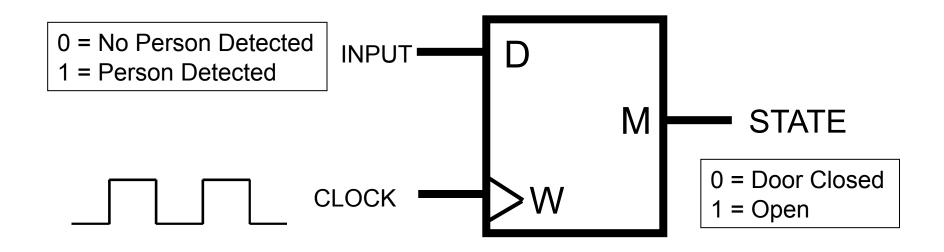

## Recall from last lecture:

"Register" with 4 bits of memory

How can you set up an addressing system for large banks of memory?

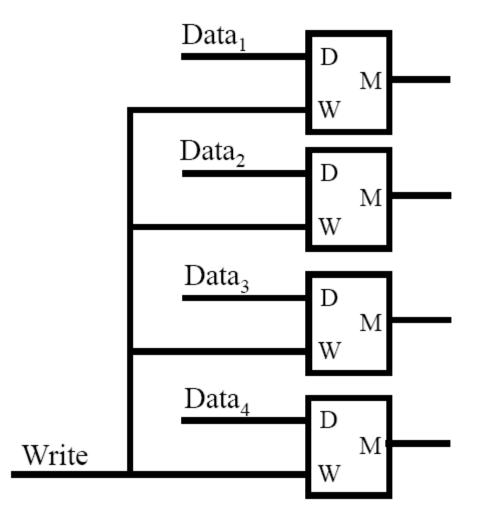

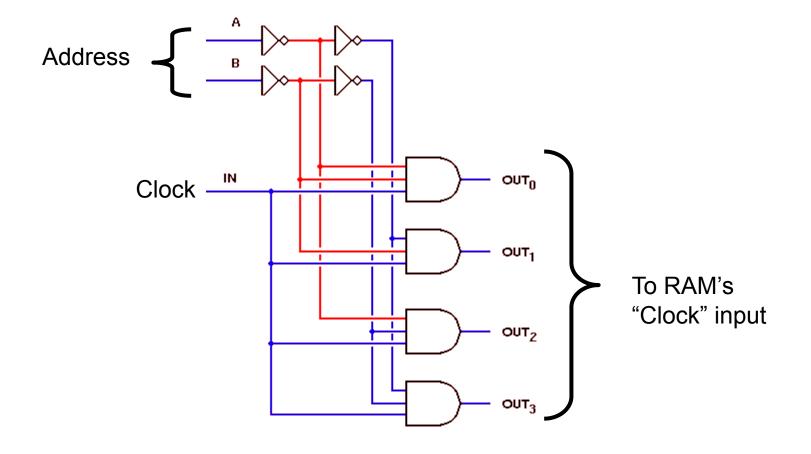

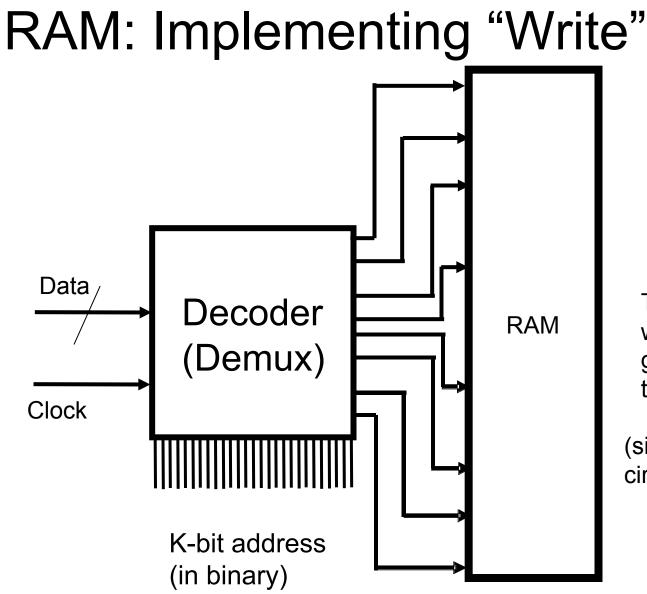

## If 4 locations, "address" has 2 bits

The decoder selects which cell in the RAM gets its "Write" input toggled

(simple combinational circuit; see logic handout)

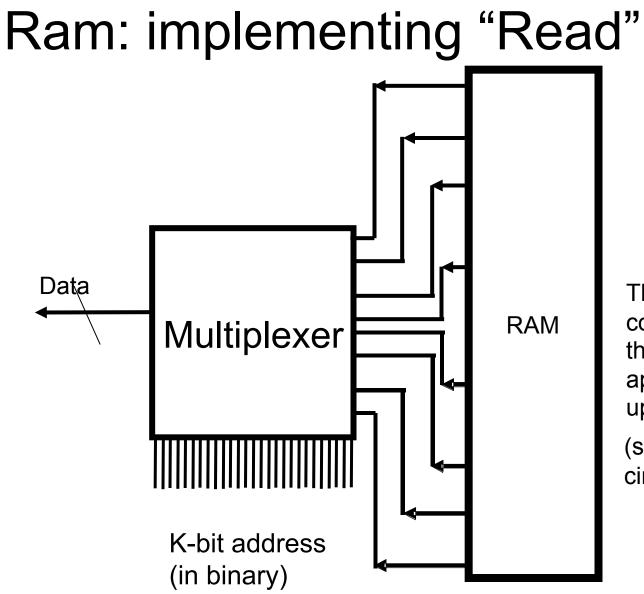

The multiplexer is connected to all cells in the RAM; selects the appropriate cell based upon the k-bit address

(simple combinational circuit; see logic handout)

## Next, the secret revealed...

## How computers execute programs.

CPU = Central Processing Unit

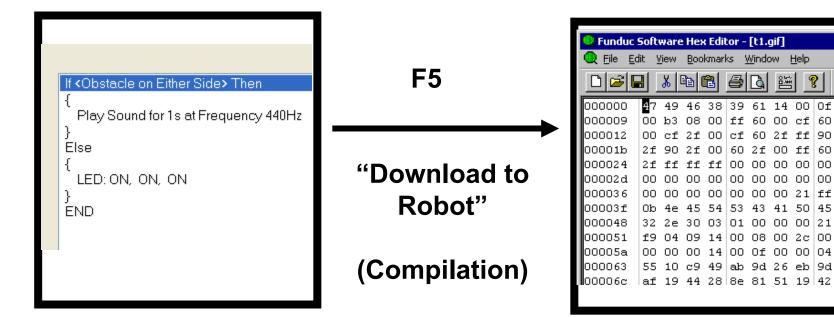

#### Scribbler Control **Panel Program**

#### Machine **Executable Code**

Point 1: Programs are "translated" into "machine language"; this is what's get executed.

Similar to:

T-P programs represented in binary

14 00 Of

cf 60

ff 60

00 00

21 ff

19 42

00 20 00

00

• .exe files in the Wintel world

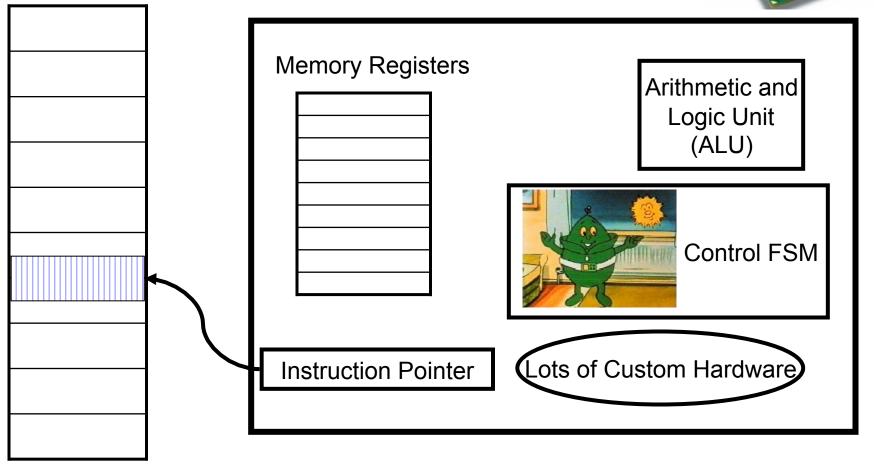

# Greatly simplified view of modern CPUs.

inte

Program (in binary) stored in memory

RAM

### **Examples of Machine Language Instructions**

| ADD  | 12 | 37    | Add contents of Register<br>3 and Register 7 and<br>store in Register 12 |

|------|----|-------|--------------------------------------------------------------------------|

| LOAD | 3  | 67432 | Read Location 67432<br>from memory and load<br>into Register 3           |

| JUMP | 4  | 35876 | If register 4 has a<br>number > 0 set IP to<br>35876                     |

Stored in binary (recall Davis's binary encoding of T-P programs)

# Different CPUs have different machine languages

- Intel Pentium, Core, Xeon, etc. (PC, recent Mac)

- Power PC (old Mac)

- ARM (cellphones, mobile devices, etc.)

"Backwards Compatibility" – Core 2's machine language extends Pentium's machine language

Machine languages now allow complicated calculations (eg for multimedia, graphics) in a single instruction

# Main Insight

# Computer = FSM controlling a larger (or infinite) memory.

# Meet the little green man..

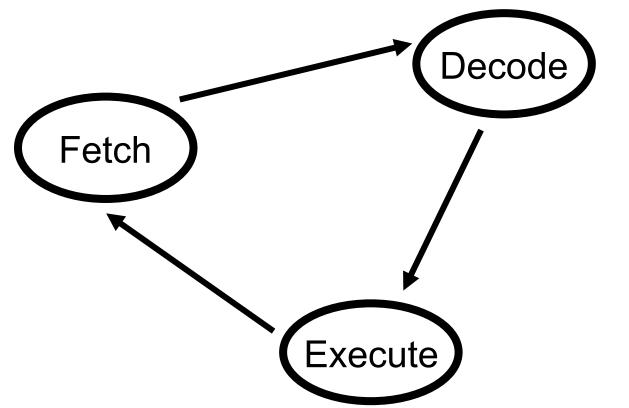

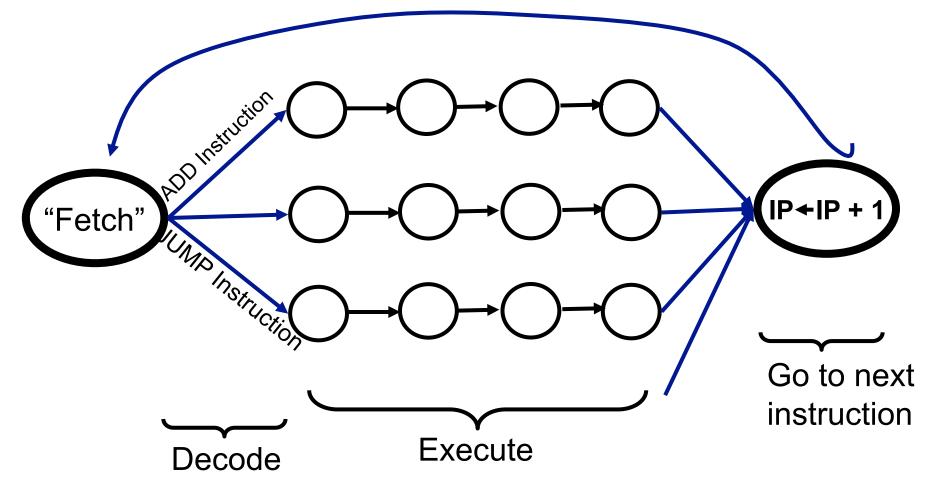

The Fetch – Decode – Execute FSM

## Fetch – Decode – Execute FSM

## CPU as a conductor of a symphony

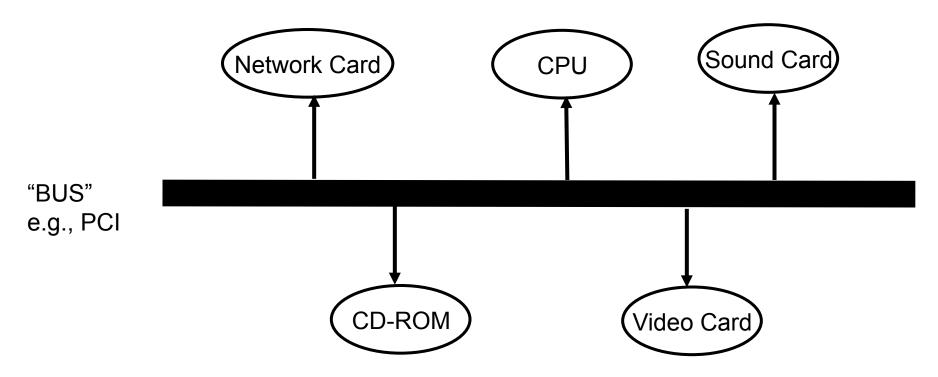

### Bus: "Everybody hears everybody else"

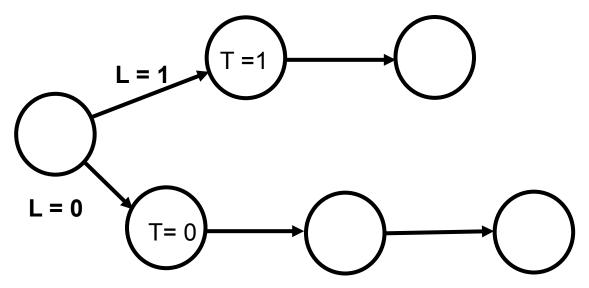

# How an FSM does "reasoning"

"If left infrared sensor detects a person, turn left"

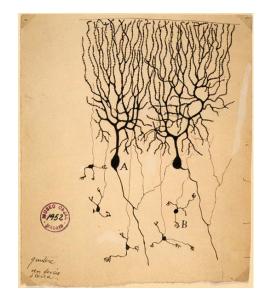

## **Speculation: Brain as FSM?**

- Network ("graph") of 100 billion neurons; each connected to a few thousand others

- Neuron = tiny Computational Element;

"switching time" 0.01 s

- Neuron generates a voltage spike depending upon how many neighbors are spiking.