# CS 126 Lecture A5: **Computer Architecture**

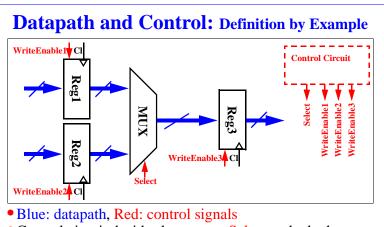

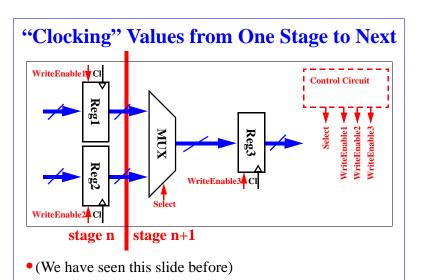

- Control circuit decides how to set Select and whether to enable WriteEnable3

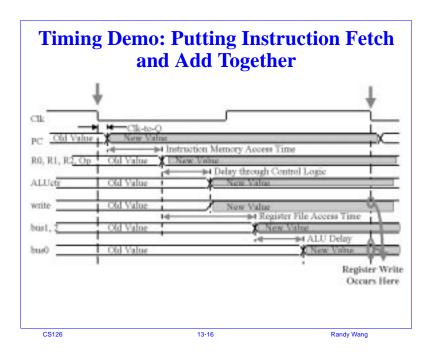

- When clock ticks

- One of Reg1 or Reg2 gets copied to Reg3 if WriteEnable3 is on

13-6

- Nothing gets copied to Reg3 if WriteEnable3 is off

13-10

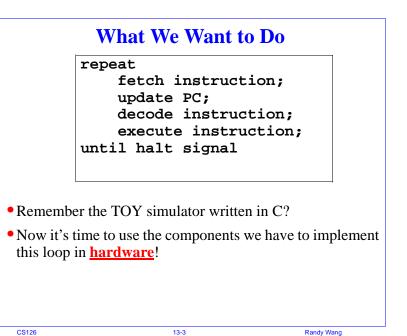

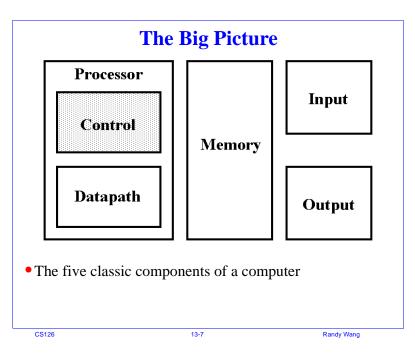

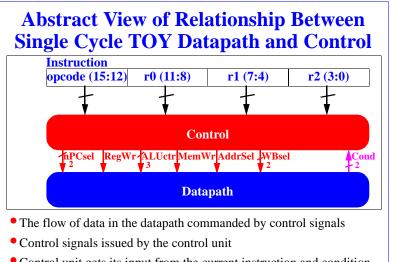

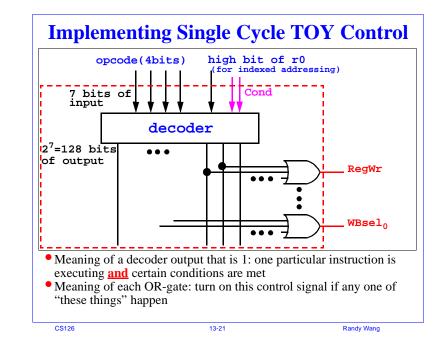

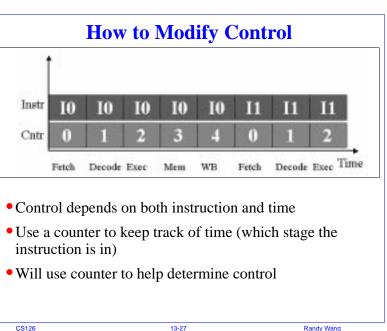

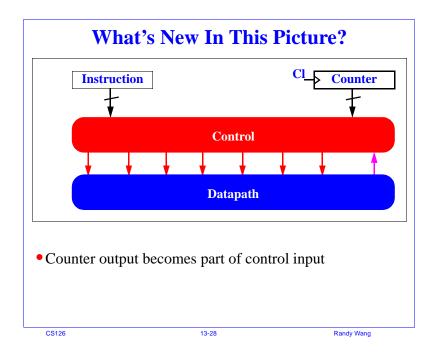

• Control unit gets its input from the current instruction and condition codes from the datapath

13-20

• Control unit is nothing but a big combinational circuit

Randy Wang

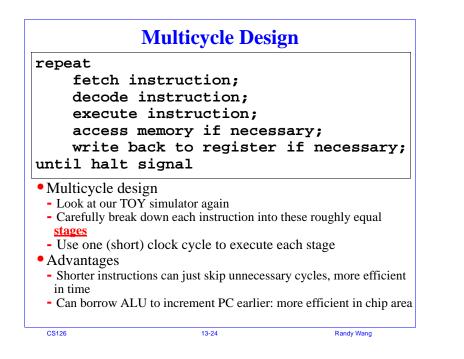

## **Problems with Single-Cycle** Implementation

- Not all instructions are equal, some longer, some shorter

- Memory accesses can be a lot longer

- The slowest instruction determines cycle time

- The processor sits idle for faster instructions

- Waste of chip area, for example:

- Need an adder to compute PC+=4 in addition to the ALU

- Could in theory eliminate the adder and borrow ALU when it's

- But in a single cycle, we can't tell when ALU is done

CS126

13-23

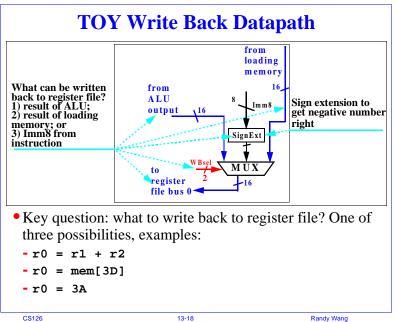

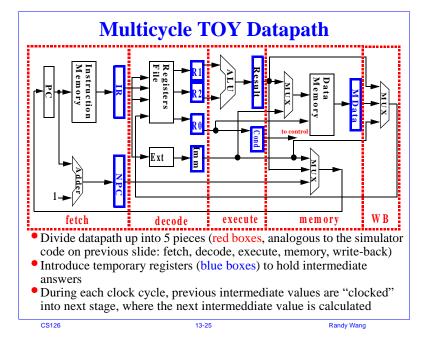

• The trick is to figure out how and when to set the control signals!

13-26

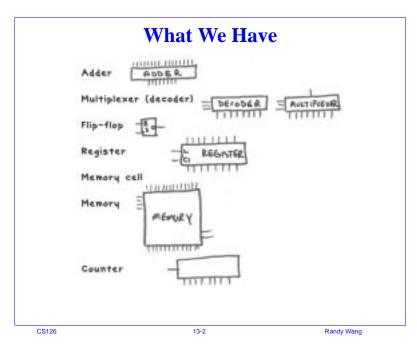

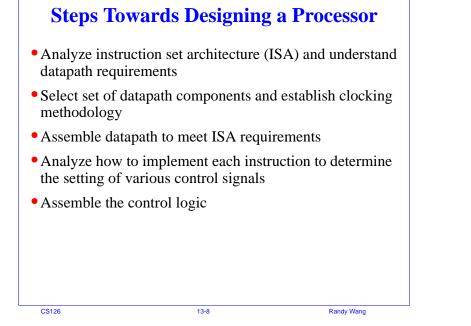

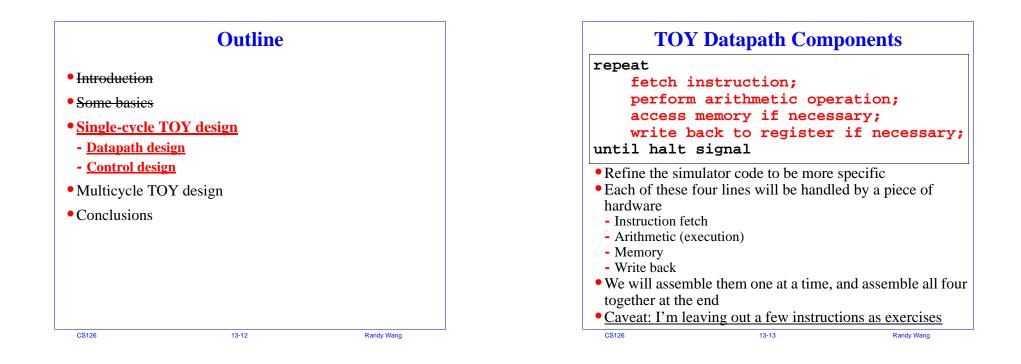

#### **Steps Towards Designing a Processor**

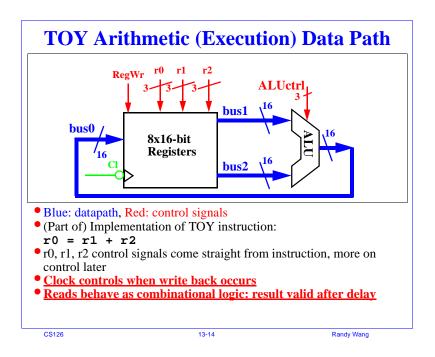

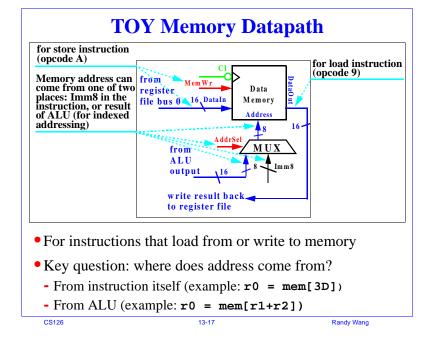

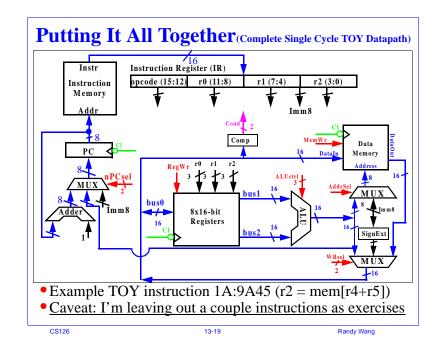

- Analyze instruction set architecture (ISA) and understand datapath requirements

- Select set of datapath components and establish clocking methodology

- Assemble datapath to meet ISA requirements

- Analyze how to implement each instruction to determine the setting of various control signals

13-30

• Assemble the control logic

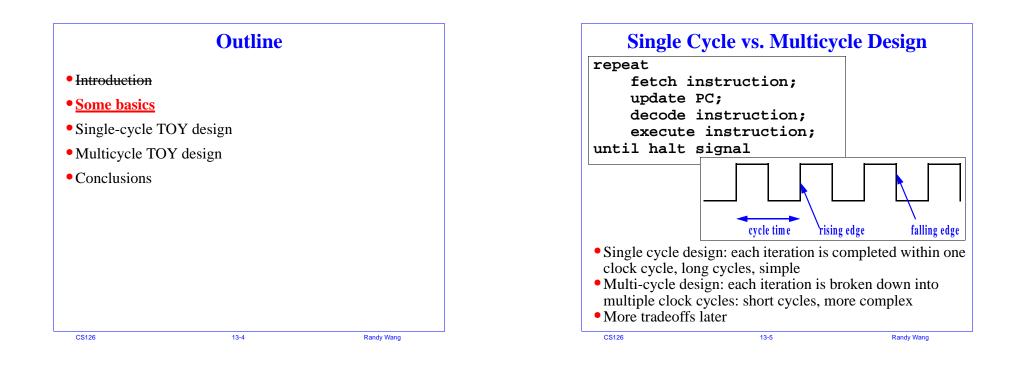

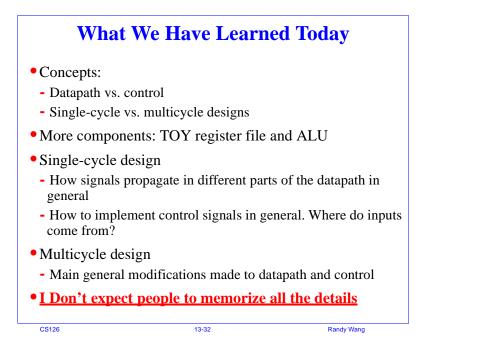

## Where's the Science? Understanding Tradeoffs

- We saw a deceptively trivial tradeoff today: clocking methodology

- Single cycle architecture vs. multicycle architecture

- Multicycle sounds obviously superior, right?

- Extra temporary registers and extra control logic of latter

- + Introduce time overhead

- + Introduce chip area overhead

- + Introduce extra complexity, cost, time-to-market, .....

- The question to a computer architect is whether this tradeoff is worth it

- More complex tradeoffs at each step of the prev. slide

- Nice to hide all this under the hood of an ISA

CS126

Randy Wang

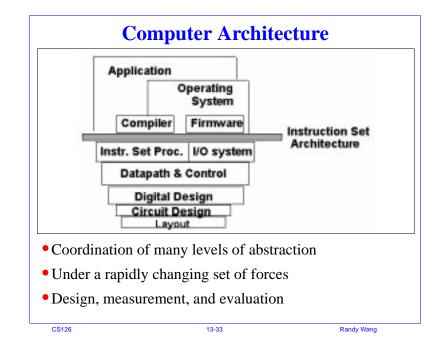

# **Dramatic Technology Change**

- Technology

- <u>Processor</u> logic capacity: +30% / yr; clock rate: +20% / yr; overall performance: ~+60% / yr!

- Memory and disk capacity: ~+60% / yr

- Numbers, though impressive, are boring. What's really exciting is revolutionary leaps in applications!

- Quantitative improvement and revolutionary leaps interleave as technology advances

- ~1985: <u>Single-chip</u> (32-bit) <u>processors</u> and <u>single-board</u> <u>computers</u> emerged, led to revolutions in all aspects of computer science!

- Conjecture: ~2002: Emergence of powerful <u>single-chip</u> <u>systems</u>, what will be its implication?!