3

sequential circuit: loops allowed (stay tuned)

#### Context

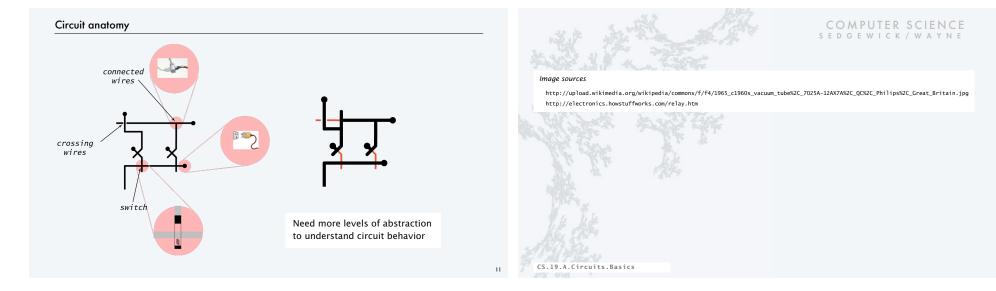

- Q. What is a combinational circuit?

- A. A digital circuit (all signals are 0 or 1) with no feedback (no loops).

analog circuit: signals vary continuously

- Q. Why combinational circuits?

- A. Accurate, reliable, general purpose, fast, cheap.

- **Basic abstractions**

- On and off.

- Wire: propagates on/off value.

- Switch: controls propagation of on/off values through wires.

Applications. Smartphone, tablet, game controller, antilock brakes, microprocessor, ...

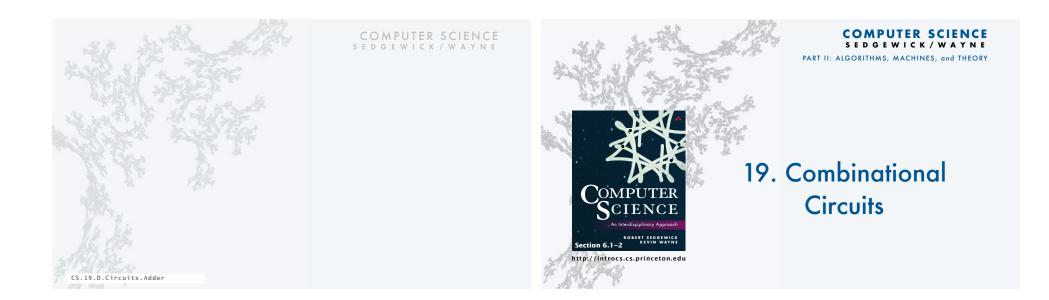

### Wires

### Wires propagate on/off values

- ON (1): connected to power.

- OFF (0): not connected to power.

- Any wire connected to a wire that is ON is also ON.

- Drawing convention: "flow" from top, left to bottom, right.

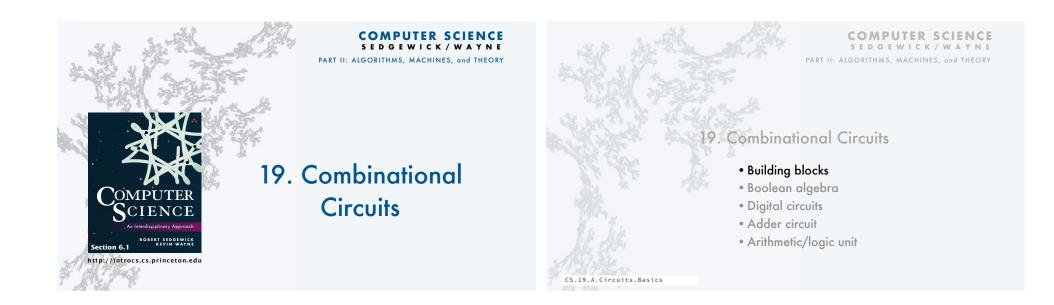

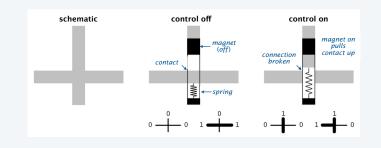

# **Controlled Switch**

### Switches control propagation of on/off values through wires.

- Simplest case involves two connections: control (input) and output.

- control OFF: output ON

- control ON: output OFF

# **Controlled Switch**

### Switches control propagation of on/off values through wires.

- General case involves *three* connections: control input, *data input* and output.

- control OFF: output is connected to input

- control ON: output is disconnected from input

Idealized model of pass transistors found in real integrated circuits.

### Controlled switch: example implementation

### A relay is a physical device that controls a switch with a magnet

- 3 connections: input, output, control.

- Magnetic force pulls on a contact that cuts electrical flow.

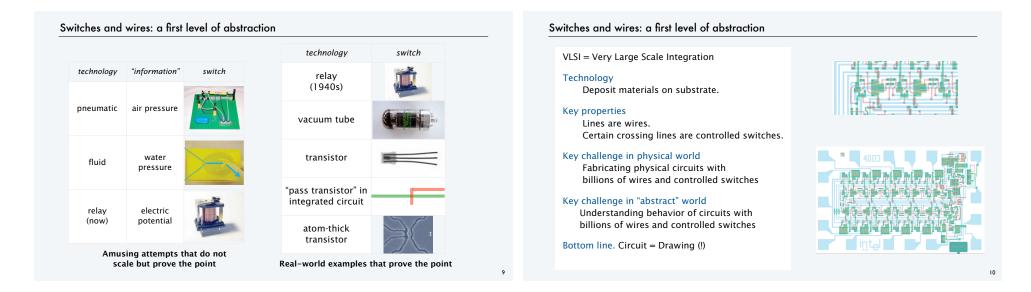

# First level of abstraction

Switches and wires model provides separation between physical world and logical world.

- We assume that switches operate as specified.

- That is the only assumption.

- Physical realization of switch is irrelevant to design.

Physical realization dictates performance

- Size.

- Speed.

- Power.

New technology immediately gives new computer.

Better switch? Better computer.

Basis of Moore's law.

# Boolean algebra

Developed by George Boole in 1840s to study logic problems

• Variables represent *true* or *false* (1 or 0 for short).

• Basic operations are AND, OR, and NOT (see table below). Widely used in mathematics, logic and computer science.

| operation | Java notation | logic notation | circuit design<br>(this lecture) |                                   |

|-----------|---------------|----------------|----------------------------------|-----------------------------------|

| AND       | х && у        | $x \wedge y$   | xy                               |                                   |

| OR        | х    у        | $x \lor y$     | x + y                            | various notation<br>in common use |

| NOT       | ! x           | ¬ <i>x</i>     | <i>x</i> '                       |                                   |

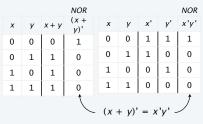

DeMorgan's Laws

(xy)' = (x' + y')

(x + y)' = x'y'

Example: (stay tuned for proof)

Relevance to circuits. Basis for next level of abstraction.

#### Truth tables

A truth table is a systematic way to define a Boolean function

- One row for each possible set of arguments.

- Each row gives the function value for the specified arguments.

- *N* inputs: 2<sup>*N*</sup> rows needed.

| x | <i>x</i> ' | x   | y | xy | x  | y | x + y |  | x | y   | NOR | x | y   | XOR |

|---|------------|-----|---|----|----|---|-------|--|---|-----|-----|---|-----|-----|

| 0 | 1          | 0   | 0 | 0  | 0  | 0 | 0     |  | 0 | 0   | 1   | 0 | 0   | 0   |

| 1 | 0          | 0   | 1 | 0  | 0  | 1 | 1     |  | 0 | 1   | 0   | 0 | 1   | 1   |

| N | от         | 1   | 0 | 0  | 1  | 0 | 1     |  | 1 | 0   | 0   | 1 | 0   | 1   |

|   |            | 1   | 1 | 1  | 1  | 1 | 1     |  | 1 | 1   | 0   | 1 | 1   | 0   |

|   |            | AND |   |    | OR |   |       |  |   | NOR |     |   | XOR |     |

# Truth table proofs

Truth tables are convenient for establishing identities in Boolean logic

- One row for each possibility.

- Identity established if columns match.

# Proofs of DeMorgan's laws

| x                 | y      | xy |   |   |   |   |   | x' + y'          |  |  |  |  |

|-------------------|--------|----|---|---|---|---|---|------------------|--|--|--|--|

| 0                 | 0      | 0  | 1 | 0 | 0 | 1 | 1 | 1<br>1<br>1<br>0 |  |  |  |  |

| 0                 | 0<br>1 | 0  | 1 | 0 | 1 | 1 | 0 | 1                |  |  |  |  |

| 1                 |        | 0  | 1 | 1 | 0 | 0 | 1 | 1                |  |  |  |  |

| 1                 | 1      |    | 0 | 1 | 1 | 0 | 0 | 0                |  |  |  |  |

| (xy)' = (x' + y') |        |    |   |   |   |   |   |                  |  |  |  |  |

# All Boolean functions of two variables

- Q. How many Boolean functions of two variables?

- A. 16 (all possibilities for the 4 bits in the truth table column).

#### Truth tables for all Boolean functions of 2 variables

| x | y | ZERO | AND |   | x |   | y | XOR | OR | NOR | EQ | $\neg y$ |   | ¬ <i>x</i> |   | NAND | ONE |

|---|---|------|-----|---|---|---|---|-----|----|-----|----|----------|---|------------|---|------|-----|

| 0 | 0 | 0    | 0   | 0 | 0 | 0 | 0 | 0   | 0  | 1   | 1  | 1        | 1 | 1          | 1 | 1    | 1   |

| 0 | 1 | 0    | 0   | 0 | 0 | 1 | 1 | 1   | 1  | 0   | 0  | 0        | 0 | 1          | 1 | 1    | 1   |

| 1 | 0 | 0    | 0   | 1 | 1 | 0 | 0 | 1   | 1  | 0   | 0  | 1        | 1 | 0          | 0 | 1    | 1   |

| 1 | 1 | 0    | 1   | 0 | 1 | 0 | 1 | 0   | 1  | 0   | 1  | 0        | 1 | 0          | 1 | 0    | 1   |

# Functions of three and more variables

### Q. How many Boolean functions of three variables?

A. 256 (all possibilities for the 8 bits in the truth table column).

|                                       |       |      |     |    |     |     |       |                                 |        | all extend to N variables                    |

|---------------------------------------|-------|------|-----|----|-----|-----|-------|---------------------------------|--------|----------------------------------------------|

| x                                     | У     | z    | AND | OR | NOR | MAJ | ODD   | Examples                        |        | ↓                                            |

| 0                                     | 0     | 0    | 0   | 0  | 1   | 0   | 0     | AND logica                      | al AND | 0 iff any inputs is 0 (1 iff all inputs 1)   |

| v                                     | Ŭ     | •    | Ŭ   | v  | -   | Ŭ   | Ŭ     | OR logic                        | al OR  | 1 iff any input is 1 (0 iff all inputs 0)    |

| 0                                     | 0     | 1    | 0   | 1  | 0   | 0   | 1     | NOR logic                       | al NOR | 0 iff any input is 1 (1 iff all inputs 0)    |

| 0                                     | 1     | 0    | 0   | 1  | 0   | 0   | 1     | MAJ maj                         | jority | 1 iff more inputs are 1 than 0               |

| -                                     | _     | -    | -   |    | -   | -   | -     | ODD odd                         | parity | 1 iff an odd number of inputs are 1          |

| 0                                     | 1     | 1    | 0   | 1  | 0   | 1   | 0     |                                 |        |                                              |

| 1                                     | 0     | 0    | 0   | 1  | 0   | 0   | 1     | Q. How ma                       | ny Boo | blean functions of N variables?              |

| 1                                     | 0     | 1    | 0   | 1  | 0   | 1   | 0     |                                 | Ν      | number of Boolean functions with N variables |

| 1                                     | 1     | 0    | 0   | 1  | 0   | 1   | 0     |                                 | 2      | 24 = 16                                      |

| -                                     | -     | Ŭ    | Ŭ   | -  | Ŭ   | -   | Ŭ     | a = a(2N)                       | 3      | 2 <sup>8</sup> = 256                         |

| 1                                     | 1     | 1    | 1   | 1  | 0   | 1   | 1     | A. 2 <sup>(2<sup>N</sup>)</sup> | 4      | 216 = 65,536                                 |

|                                       | . Dee | leen |     |    |     |     | ahlaa |                                 | 5      | 2 <sup>32</sup> = 4,294,967,296              |

| Some Boolean functions of 3 variables |       |      |     |    |     |     |       |                                 |        | 264 = 18,446,744,073,709,551,616             |

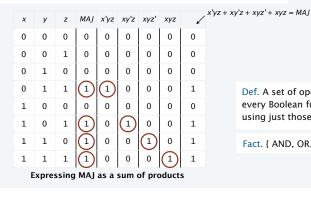

# Universality of AND, OR and NOT

Every Boolean function can be represented as a sum of products

• Form an AND term for each 1 in Boolean function.

• OR all the terms together.

Def. A set of operations is *universal* if every Boolean function can be expressed using just those operations. 17

Fact. { AND, OR, NOT } is universal.

| boolean<br>function | notation            | truth table                             | classic<br>symbol  | our symbol                                                                           | under the cover<br>circuit (gate) | proof                         |

|---------------------|---------------------|-----------------------------------------|--------------------|--------------------------------------------------------------------------------------|-----------------------------------|-------------------------------|

| NOT                 | <i>x</i> '          | x x'<br>0 1<br>1 0                      | x — • • - x'       | x – – – x'                                                                           | x 💉 x'                            | 1 iff x is 0                  |

| NOR                 | (x + y)'            | x y NOR   0 0 1   0 1 0   1 0 0   1 1 0 | x - y - y - (x+y)' | $\frac{x \ y}{NOR} - (x+y)$                                                          | (x+y)                             | y 1 iff x and y<br>are both 0 |

| OR                  | <i>x</i> + <i>y</i> | x y OR   0 0 0   0 1 1   1 0 1   1 1 1  | x - y x+y          | $\begin{array}{c} x  y \\ \mathbf{I}  \mathbf{I} \\ \mathbf{OR} \end{array} - x + y$ |                                   | x + y = ((x + y))             |

| AND                 | xy                  | x y AND   0 0 0   0 1 0   1 0 0   1 1 1 | x = -xy            | x y<br>I I<br>ANDxy                                                                  | x y<br>x y<br>x y<br>xy           | xy = (x' + y)                 |

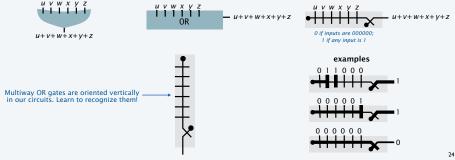

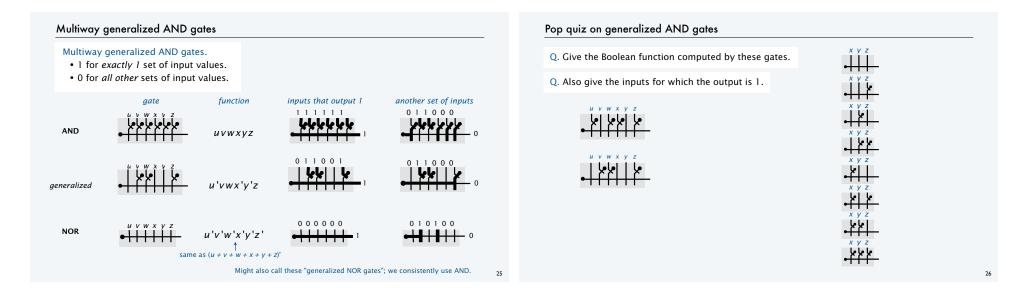

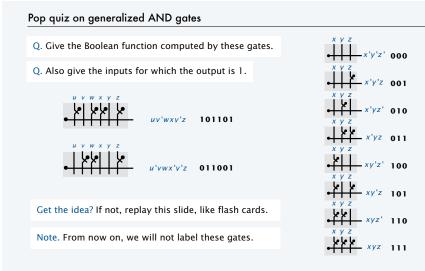

# Multiway OR gates OR gates with multiple inputs. • 1 if any input is 1. • 0 if *all* inputs are 0. classic symbol our symbol under the cover u v w x y z

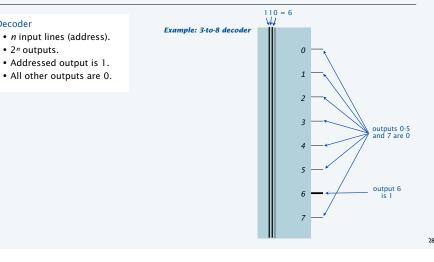

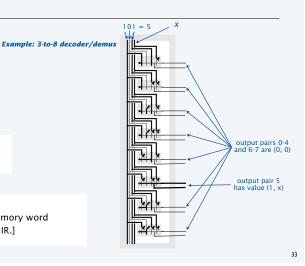

#### A useful combinational circuit: decoder

Decoder

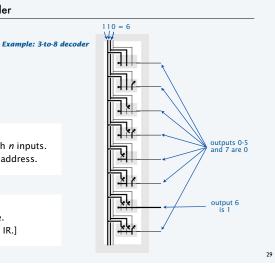

# A useful combinational circuit: decoder

#### Decoder

- *n* input lines (address).

- 2<sup>n</sup> outputs.

- Addressed output is 1.

- All other outputs are 0.

### Implementation

- Use all 2<sup>n</sup> generalized AND gates with *n* inputs.

- Only one of them matches the input address.

### Application (next lecture)

- Select a memory word for read/write.

- [Use address bits of instruction from IR.]

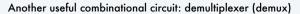

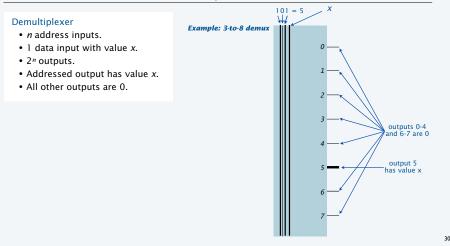

# Another useful combinational circuit: demultiplexer (demux)

#### Demultiplexer

- n address inputs.

- 1 data input with value x.

- 2<sup>n</sup> outputs.

- Addressed output has value x.

- All other outputs are 0.

# Implementation

- Start with decoder.

- Add AND x to each gate.

### Application (next lecture)

- Turn on control wires to implement instructions.

- [Use opcode bits of instruction in IR.]

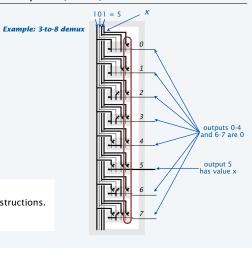

# Decoder/demux

# Decoder/demux

- *n* address inputs.

- 1 data input with value x.

- 2<sup>n</sup> output pairs.

- Addressed output *pair* has value (1, *x*).

- All other outputs are 0.

### Decoder/demux

#### Decoder/demux

- n address inputs.

- 1 data input with value x.

- 2<sup>n</sup> output pairs.

- Addressed output *pair* has value (1, *x*).

- All other outputs are 0.

#### Implementation

• Add decoder output to demux.

#### Application (next lecture)

- Access and control write of memory word

- [Use addr bits of instruction in IR.]

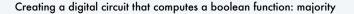

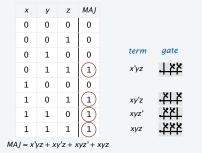

#### Use the truth table

- Identify rows where the function is 1.

- Use a generalized AND gate for each.

- OR the results together.

#### **Example 1: Majority function**

# Creating a digital circuit that computes a boolean function: odd parity

#### Use the truth table • Identify rows where the function is 1. • Use a generalized AND gate for each. • OR the results together. multiwav **Example 2: Odd parity function** OR gate ODD х z 0 0 0 0 term gate (1)ЩĶ 0 0 1 x'y'z 나지 0 1 0 (1)x'yz'0 1 0 1 (1)1 0 0 -411xy'z' 1 0 1 0 1 1 0 0 (1)<u>. XXX</u> 1 1 1 xyz ODD is 0 ODD ODD = x'y'z + x'yz' + xy'z' + xyzexample odd parity circuit

### Combinational circuit design: Summary

Problem: Design a circuit that computes a given boolean function.

### Ingredients

- OR gates.

- NOT gates. 🔨

- NOR gates. Use to make generalized AND gates

- Wire.

ODD

35

#### Method

- Step 1: Represent input and output with Boolean variables.

- Step 2: Construct truth table to define the function.

- Step 3: Identify rows where the function is 1.

- Step 4: Use a generalized AND for each and OR the results.

Bottom line (profound idea): Yields a circuit for ANY function. Caveat: Circuit might be huge (stay tuned).

| x | y | z | MAJ | x | y | z | ODD |

|---|---|---|-----|---|---|---|-----|

| 0 | 0 | 0 | 0   | 0 | 0 | 0 | 0   |

| 0 | 0 | 1 | 0   | 0 | 0 | 1 |     |

| 0 | 1 | 0 | 0   | 0 | 1 | 0 |     |

| 0 | 1 | 1 |     | 0 | 1 | 1 | 0   |

| 1 | 0 | 0 | 0   | 1 | 0 | 0 |     |

| 1 | 0 | 1 |     | 1 | 0 | 1 | 0   |

| 1 | 1 | 0 |     | 1 | 1 | 0 | 0   |

| 1 | 1 | 1 |     | 1 | 1 | 1 |     |

# Pop quiz on combinational circuit design

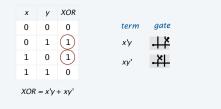

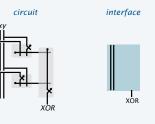

# Q. Design a circuit to implement XOR(x, y).

# Pop quiz on combinational circuit design

Q. Design a circuit to implement XOR(x, y).

# A. Use the truth table

- Identify rows where the function is 1.

- Use a generalized AND gate for each.

- OR the results together.

#### XOR function

38

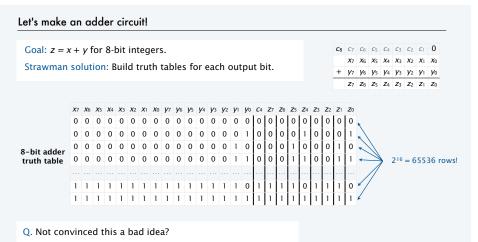

A. 128-bit adder: 2<sup>256</sup> rows >> # electrons in universe!

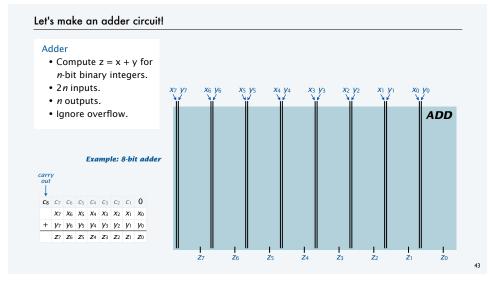

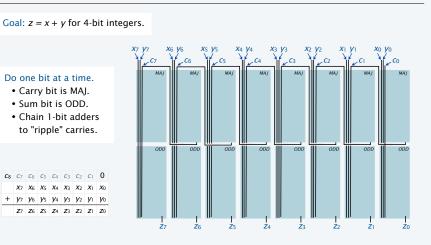

| Goal: z = | x +   | <i>y</i> for | 8-bi  | it inte              | gers.  |                |      |            |    | <b>C</b> 8 | C7                       | С6 | C5 | С4         | Сз | C2 | Cı | 0  |

|-----------|-------|--------------|-------|----------------------|--------|----------------|------|------------|----|------------|--------------------------|----|----|------------|----|----|----|----|

| Do one b  | it at | a tin        | ne.   |                      |        | A surprise!    |      |            |    |            | <b>X</b> 7               |    |    |            |    |    |    |    |

| • Build   | truth | ı tab        | le fo | r carr               | y bit. | Carry bit is I | MAJ. |            |    | +          | <b>y</b> 7<br><b>Z</b> 7 | _  | _  | _          | _  | -  | _  | -  |

| • Build   |       |              |       |                      |        | • Sum bit is O | -    |            |    |            | 27                       | 26 | 25 | <b>Z</b> 4 | 23 | 22 | 21 | 20 |

|           |       |              |       |                      |        |                |      |            |    |            |                          |    |    |            |    |    |    |    |

|           | Xi    | <b>y</b> i   | Ci    | <b>C</b> <i>i</i> +1 | MAJ    |                | Xi   | <b>y</b> i | Ci | Zi         | 0                        | DD | )  |            |    |    |    |    |

|           | 0     | 0            | 0     | 0                    | 0      |                | 0    | 0          | 0  | 0          |                          | 0  |    |            |    |    |    |    |

|           | 0     | 0            | 1     | 0                    | 0      |                | 0    | 0          | 1  | 1          |                          | 1  |    |            |    |    |    |    |

|           | 0     | 1            | 0     | 0                    | 0      |                | 0    | 1          | 0  | 1          |                          | 1  |    |            |    |    |    |    |

| carry bit | 0     | 1            | 1     | 1                    | 1      | sum bit        | 0    | 1          | 1  | 0          |                          | 0  |    |            |    |    |    |    |

|           | 1     | 0            | 0     | 0                    | 0      |                | 1    | 0          | 0  | 1          |                          | 1  |    |            |    |    |    |    |

|           | 1     | 0            | 1     | 1                    | 1      |                | 1    | 0          | 1  | 0          |                          | 0  |    |            |    |    |    |    |

|           | 1     | 1            | 0     | 1                    | 1      |                | 1    | 1          | 0  | 0          |                          | 0  |    |            |    |    |    |    |

|           | 1     | 1            | 1     | 1                    | 1      |                | 1    | 1          | 1  | 1          |                          | 1  |    |            |    |    |    |    |

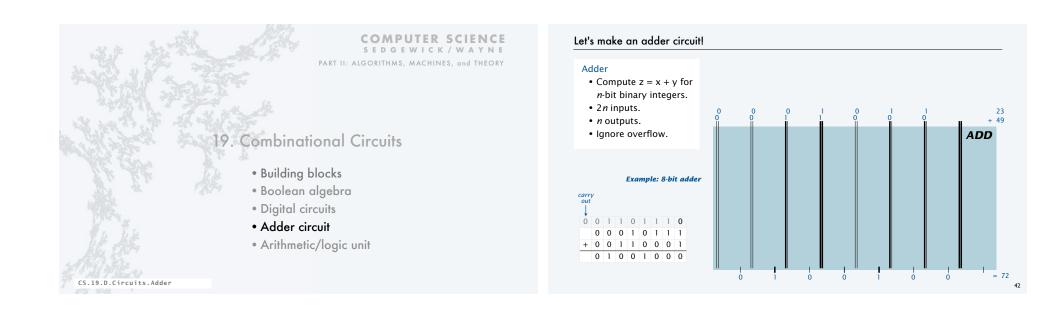

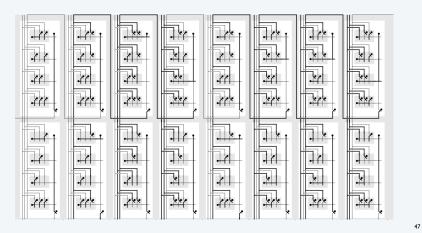

# Let's make an adder circuit!

### An 8-bit adder circuit

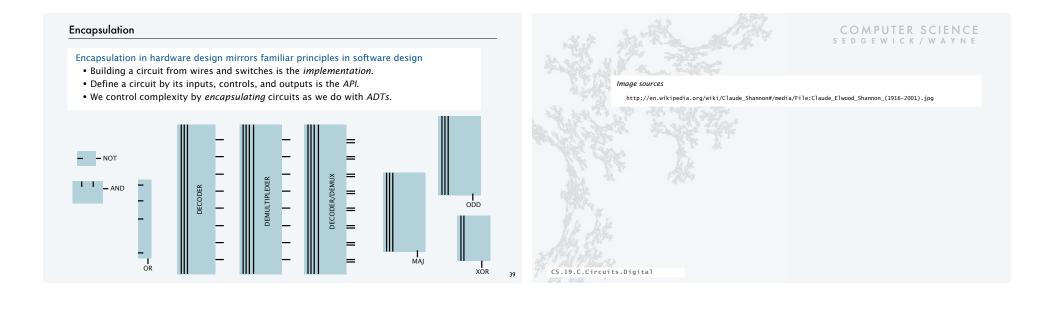

# Layers of abstraction

### Lessons for software design apply to hardware

- Interface describes behavior of circuit.

- Implementation gives details of how to build it.

- Exploit understanding of behavior at each level.

# Layers of abstraction apply with a vengeance

- On/off.

- Controlled switch. [relay, pass transistor]

- Gates. [NOT, OR, AND]

- Boolean functions. [MAJ, ODD]

- Adder.

- Arithmetic/Logic unit (next).

- CPU (next lecture, stay tuned).

Vastly simplifies design of complex systems and enables use of new technology at any layer

48

51

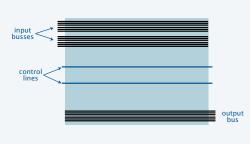

# Next layer of abstraction: modules, busses, and control lines

Basic design of our circuits

- Organized as modules (functional units of TOY: ALU, memory, register, PC, and IR).

- Connected by *busses* (groups of wires that propagate information between modules).

- Controlled by *control lines* (single wires that control circuit behavior).

#### Conventions

- Bus inputs are at the top, input connections are at the left.

- Bus outputs are at the bottom, output connections are at the right.

- Control lines are blue.

These conventions make circuits easy to understand. (Like style conventions in coding.)

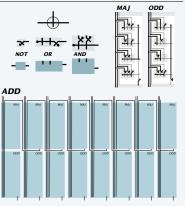

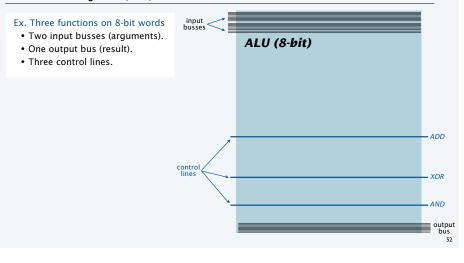

# Arithmetic and logic unit (ALU) module

# Arithmetic and logic unit (ALU) module

### Ex. Three functions on 8-bit words

- Two input busses (arguments)

- One output bus (result).

- Three control lines.

- Left-right shifter circuits omitted (see book for details).

#### Implementation

- · One circuit for each function

- Compute all values in parallel

Q. How do we select desired output?

A. "One-hot muxes" (see next slide)

"Calculator" at the heart of your computer.

| vords    | input<br>busses |   |     |          | <br>       |            |            |           |               |

|----------|-----------------|---|-----|----------|------------|------------|------------|-----------|---------------|

| ents).   |                 |   |     |          |            |            |            |           |               |

| mitted   |                 |   |     |          |            |            |            |           |               |

|          |                 |   |     |          |            |            |            |           |               |

| n.       |                 |   |     |          |            |            |            |           |               |

| lel.     | /               |   |     |          |            |            |            | **<br>Tk. | - ADD         |

| output?  | control         |   | 74) | 74<br>(* | 74-)<br>(# | 74-)<br>(# | 74.)<br>(# |           | - XOR         |

| slide).  |                 | * | *   | <b>*</b> | 7#~)<br>(# | ( 66 1     | 1 66 1     | 74-)      | - AND         |

| ur compi | uter.           |   |     |          |            | l (#       |            |           | output<br>bus |

|          | V               |   |     |          |            |            |            |           | 53            |

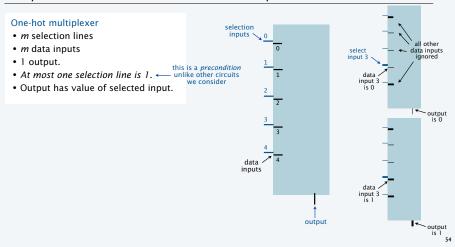

# A simple and useful combinational circuit: one-hot multiplexer

# A simple and useful combinational circuit: one-hot multiplexer

#### multiway OR gate One-hot multiplexer • *m* selection lines • *m* data inputs seler AND ag 1 output. • At most one selection line is 1. dat npu • Output has value of selected input. output is 0 Implementation • AND corresponding selection and data inputs. • OR all results (at most one is 1). Applications • Arithmetic-logic unit (previous slide). • Main memory (next lecture). input Important to note. No direct connection from input to output. output is 1 a virtual selection switch

# Summary: Useful combinational circuit modules

Next: Registers, memory, connections, and control.