Who? Stuart Feldman '68 When? 1976 Where? Bell Labs

(This is Stu Feldman recently; in 1976 he looked younger)

### **Make Command Syntax**

Command syntax

make [-f makefile] [target]

- makefile

- · Textual representation of dependency graph

- · Contains dependency rules

- Default name is makefile, then Makefile

- target

- Whatmake should build

- · Usually: .o file, or an executable binary file

- Default is first one defined in makefile

**Dependency Rules**

Dependency rule syntax

target: dependencies

<tab>command

- target: the file you want to build

- dependencies: the files on which the target depends

- command: what to execute to create the target (after a TAB character)

#### Dependency rule semantics

- Build target iff it is older than any of its dependencies

- · Use command to do the build

Work recursively; examples illustrate...

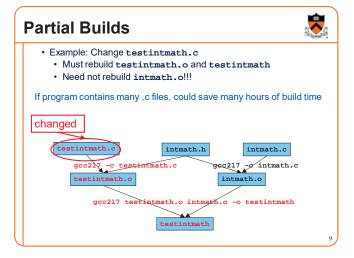

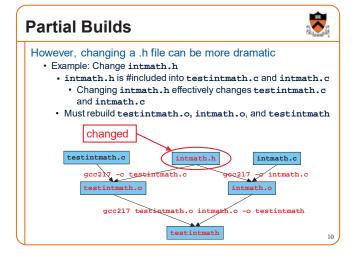

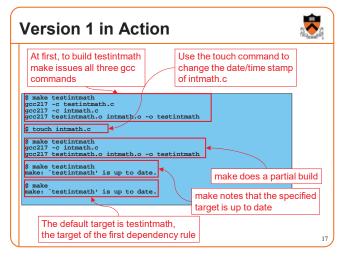

### **Makefile Version 1** testintmath.c intmath.h intmath.c gcc2N -c testintmath.c cc217 -c intmath.c intmath.o testintmath.o gcc217 testintmath.o intmath.o -o testintmath testintmath Makefile: testintmath: testintmath.o intmath.o gcc217 testintmath.d intmath.o -o testintmath testintmath.o: testintmath.c intmath.h gcc217 -c testintmath.c intmath.o: intmath.c intmath.h

## **Non-File Targets**

#### Adding useful shortcuts for the programmer

- make all: create the final executable binary file

- make clean: delete all .o files, executable binary file

- make clobber: delete all Emacs backup files, all .o files, executable binary

#### Commands in the example

- rm -f: remove files without querying the user

- Files ending in '~' and starting/ending in '#' are Emacs backup files

```

all: testintmath

clobber: clean

rm -f *~ \#*\#

clean:

rm -f testintmath *.o

```

# **Makefile Version 2**

23

```

# Dependency rules for non-file targets

all: testintmath

clobber: clean

rm -f *~ \#*\#

clean:

rm -f testintmath *.o

# Dependency rules for file targets

testintmath: testintmath.o intmath.o

gcc217 testintmath.o intmath.o -o testintmath

testintmath.o: testintmath.c intmath.h

gcc217 -c testintmath.c

intmath.o: intmath.c intmath.h

gcc217 -c intmath.c

```

```

Version 2 in Action

make observes that "clean" target

doesn't exist; attempts to build it

by issuing "rm" command

Same idea here, but

$ make clean

rm -f testintmath *.o

"clobber" depends upon "clean

$ make clobber

rm -f testintmath *.o

rm -f *~ \#*\#

$ make all

gcc217 -c testintmath.c

gcc217 -c intmath.c

gcc217 testintmath.o intmath.o -o testintmath

$ make

make: Nothing to be done for `all'.

"all" depends upon

"testintmath"

'all" is the default target

```

# **Agenda**

Motivation for Make

Make Fundamentals

Non-File Targets

#### **Macros**

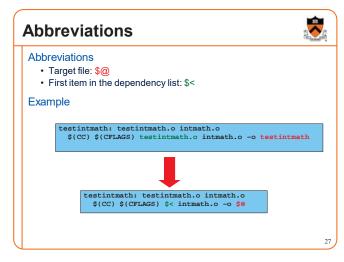

**Abbreviations**

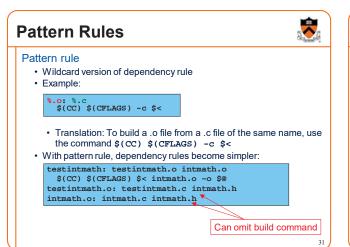

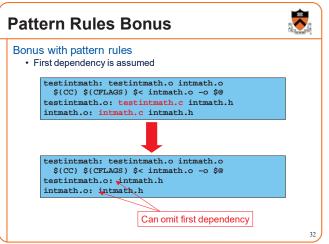

Pattern Rules

### **Macros**

#### make has a macro facility

- · Performs textual substitution

- Similar to C preprocessor's #define

#### Macro definition syntax

macroname = macrodefinition

• make replaces \$(macroname) with macrodefinition in remainder of Makefile

Example: Make it easy to change build commands

Example: Make it easy to change build flags

CFLAGS = -D NDEBUG -O

### Makefile Version 3

```

CC = gcc217

\# CC = gcc217m

CFLAGS =

# CFLAGS = -g

# CFLAGS = -D NDEBUG

# CFLAGS = -D NDEBUG -O

# Dependency rules for non-file targets

all: testintmath

clobber: clean

rm -f *~ \#*\#

clean:

rm -f testintmath *.o

# Dependency rules for file targets

testintmath: testintmath.o intmath.o

$(CC) $(CFLAGS) testintmath.o intmath.o -o testintmath

testintmath.o: testintmath.c intmath.h

$(CC) $(CFLAGS) -c testintmath.c

intmath.o: intmath.c intmath.h

$(CC) $(CFLAGS) -c intmath.c

```

# **Making Makefiles**

#### In this course

· Create Makefiles manually

### Beyond this course

- Can use tools to generate Makefiles

- See mkmf, others

**Makefile Gotchas**

#### Beware:

- Each command (i.e., second line of each dependency rule) must begin with a tab character, not spaces

- Use the rm -f command with caution

**Make Resources**

C Programming: A Modern Approach (King) Section 15.4

#### GNU make

http://www.gnu.org/software/make/manual/make.html

38

# Summary

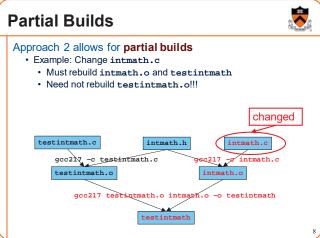

#### Motivation for Make

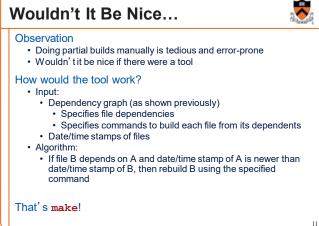

· Automation of partial builds

### Make fundamentals (Makefile version 1)

• Dependency rules, targets, dependencies, commands

Non-file targets (Makefile version 2)

Macros (Makefile version 3)

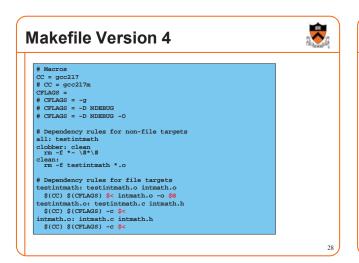

Abbreviations (Makefile version 4)

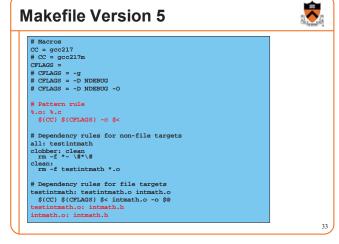

Pattern rules (Makefile version 5)

40

\_