# Topic 21: Memory Technology

COS / ELE 375

### Computer Architecture and Organization

Princeton University Fall 2015

Prof. David August

# Old Stuff Revisited Mercury Delay Line Memory

Maurice Wilkes, in 1947, with first mercury tank memories built for EDSAC.

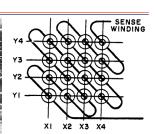

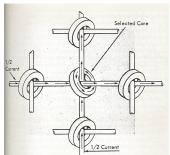

### **Core Memory**

- Theory of operation

- Threaded by hand!

- The Lifesaver connection

- Refresh

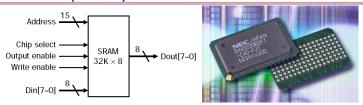

### Static RAM (SRAM)

- SRAM Fast, but not the most dense (better than core!)

- Chip select can be viewed as another address line

- Din and Dout are often combined to save pins

- Need output enable (OE\_L enable low)

- Need write enable (WE\_L enable low)

- Don't assert both write enable and output enable

- Result is unknown.

- This is bad.

- Don't do it!!!

### The Transistor Makes It Possible!

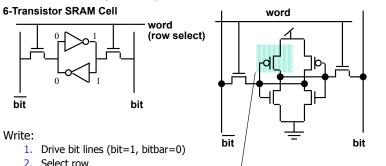

### Static RAM (SRAM) Cell

Replaced with pullup resistor

2. Select row

Read:

- 1. Precharge bit and bitbar to Vdd

- 2. Select row

- 3. Cell pulls one line low

- 4. Sense amp on column detects difference between bit and bitbar

#### Why is it Static?

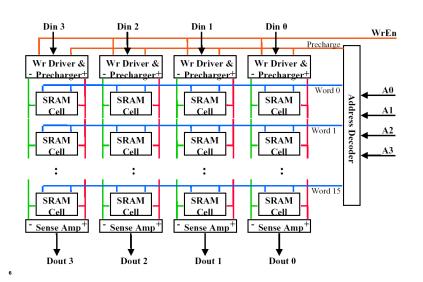

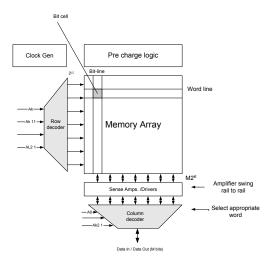

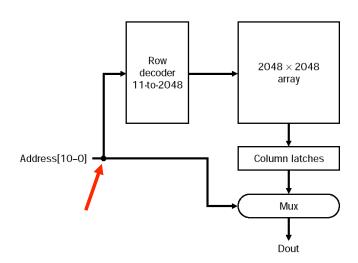

### **Typical SRAM Organization**

### **Typical SRAM Organization**

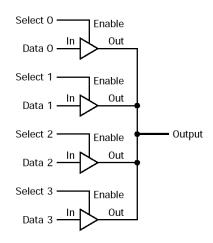

### **Three-State Buffers**

### Avoid HUGE MUX using three-state buffers

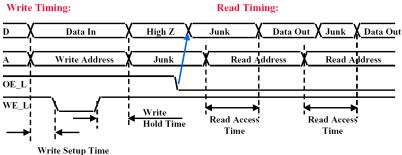

# **Typical SRAM Timing**

# Write Timing:

- Fully functional 70 Mbit SRAM chips have been made

- >0.5 billion transistors

- 0.57 μm<sup>2</sup> cell size

- Uses all process features needed for 65 nm logic products

Mark Bohr: Intel 04

### Dynamic RAM (DRAM)

- · Slower, cheaper, more dense than SRAM

- Dynamic?

11

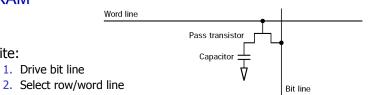

### Dynamic RAM Cell

#### DRAM

# Read:

Write:

- 1. Precharge bit line to Vdd

- 2. Select row/word line

- 3. Cell and bit line share charge

- 4. Sense (sense amp can detect changes of ~10-100k electrons)

- 5. Write: restore the value

#### Refresh (capacitor leaks):

1. Just do a dummy read to every cell.

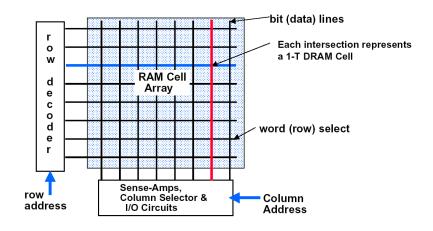

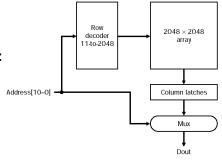

# 4Mx1 DRAM Organization

13

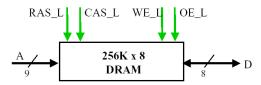

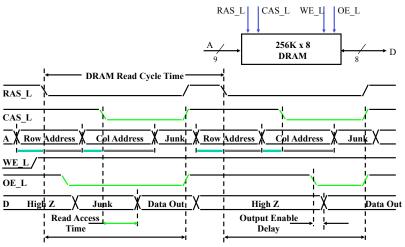

### Logic Diagram of a Typical DRAM

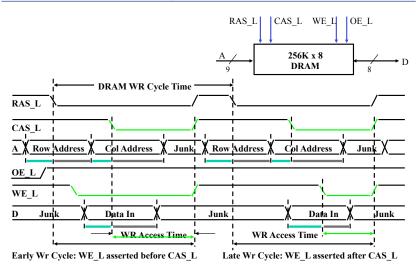

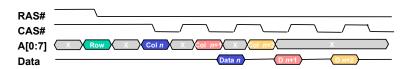

- Row and column addresses share the same pins (A)

- RAS\_L goes low: Pins A are latched in as row address

- CAS\_L goes low: Pins A are latched in as column address

- RAS/CAS edge-sensitive

- Din and Dout share the same pins (D)

- Control Signals (RAS\_L, CAS\_L, WE\_L, OE\_L) typically active low

$Early\ Read\ Cycle:\ OE\_L\ asserted\ before\ CAS\_L\qquad Late\ Read\ Cycle:\ OE\_L\ asserted\ after\ CAS\_L$

### **DRAM Write Timing**

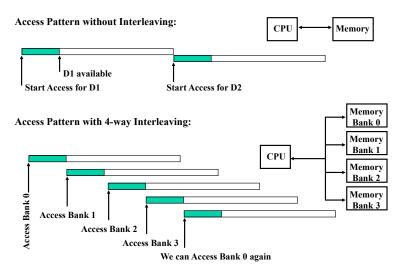

Increasing Bandwidth - Interleaving

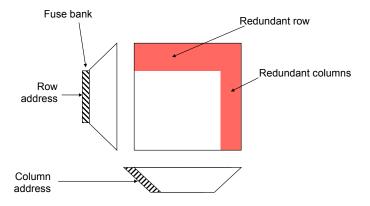

# Improving Yield with Redundancy

#### 19

### "New" DRAMs

- For decades, DRAM Interface was stable (RAS, CAS, etc.)

- Only in past decade has it begun to evolve again

- Especially in systems with few DRAM chips

Bandwidth/Througput

Ease of design

Several Enhancements:

- Page Mode

- EDO RAM

- Burst DRAM

- Synchronous DRAM

- Rambus DRAM

### **Paged Mode DRAM**

- Multiple accesses to different columns from same row

- Saves RAS and RAS to CAS delay

### **Extended Data Output RAM**

A data output latch enables to parallel next column address with current column data

#### 22

### **Burst DRAM**

· Generate a consecutive address by itself

#### 23

### Synchronous DRAM - SDRAM

- All signals are referenced to an external clock (100MHz-200MHz)

- Makes timing more precise with other system devices

- Multiple Banks

- Multiple pages open simultaneously (one per bank)

- Command driven functionality instead of signal driven

- ACTIVE: selects both the bank and the row to be activated

- ACTIVE to a new bank can be issued while accessing current bank

- READ/WRITE: select column

- Read and write accesses to the SDRAM are burst oriented

- Successive column locations accessed in the given row

- Burst length is programmable: 1, 2, 4, 8, and full-page

- Full-page burst may end with a BURST TERMINATE to get arbitrary burst lengths

- A user programmable Mode Register

- CAS latency, burst length, burst type

- Auto pre-charge: may close row at last read/write in burst

- Auto refresh: internal counters generate refresh address

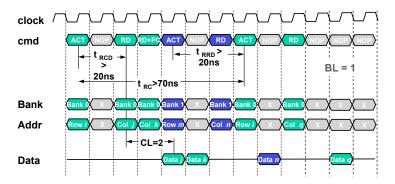

### **SDRAM Timing**

- t<sub>RCD</sub>: ACTIVE to READ/WRITE gap = [t<sub>RCD</sub>(MIN) / clock period]

- t<sub>RC</sub>: successive ACTIVE to a different row in the same bank

- t<sub>RRD</sub>: successive ACTIVE commands to different banks

25

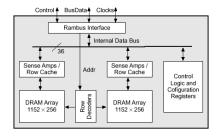

### Rambus (R)DRAM

- · Develop by Rambus Inc. and Intel

- Based on a narrow bus (16bits) runs at high speed 400Mhz

- Pipeline operation

- Multi array

- Data transfer on both edges

26

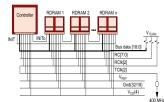

### **RDRAM System**

### Summary

### $DRAM \rightarrow slow$ , cheap, dense

- Good for BIG main memory

- Must be refreshed

### SRAM → fast, expensive, not very dense

- Good choice for fast memory like caches!

- Holds state while power applied

Memory hierarchy to get the best of both!