**COMPUTER SCIENCE** S E D G E W I C K / W A Y N E

# COMPUTER SCIENCE

An Interdisciplinary Approach

ROBERT SEDGEWICK KEVIN WAYNE

http://introcs.cs.princeton.edu

# **20.** Combinational Circuits

### **Combinational circuits**

- Q. What is a combinational circuit?

- A. A digital circuit (all signals are 0 or 1) with no feedback (no loops).

analog circuit: signals vary continuously

Q. Why combinational circuits?

A. Accurate, reliable, general purpose, fast, cheap.

### Basic abstractions

- On and off.

- Wire: propagates on/off value.

- Switch: controls propagation of on/off values through wires.

### Applications. Smartphone, tablet, game controller, antilock brakes, microprocessor, ...

sequential circuit: loops allowed (stay tuned)

### **COMPUTER SCIENCE** S E D G E W I C K / W A Y N E

### 20. Combinational Circuits

- Building blocks

- Boolean algebra

- Digital circuits

- Adder

CS.20.A.Circuits.Basics

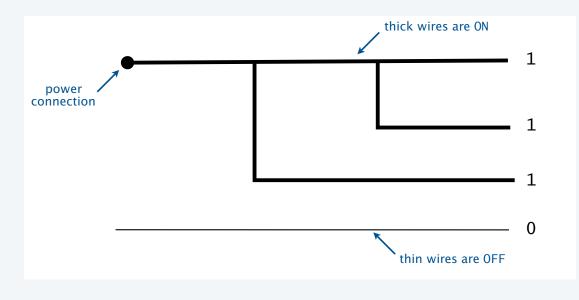

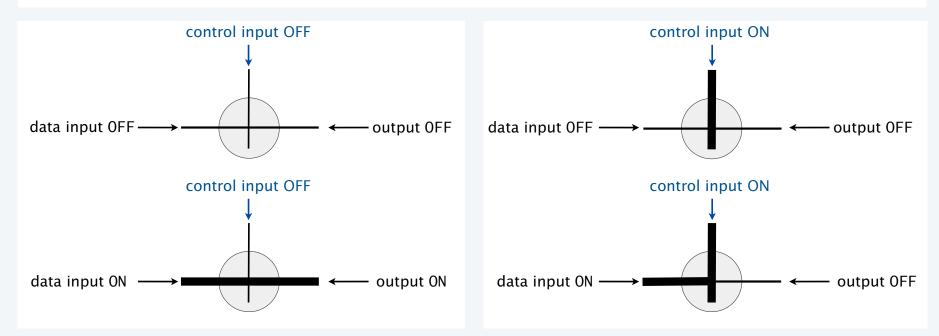

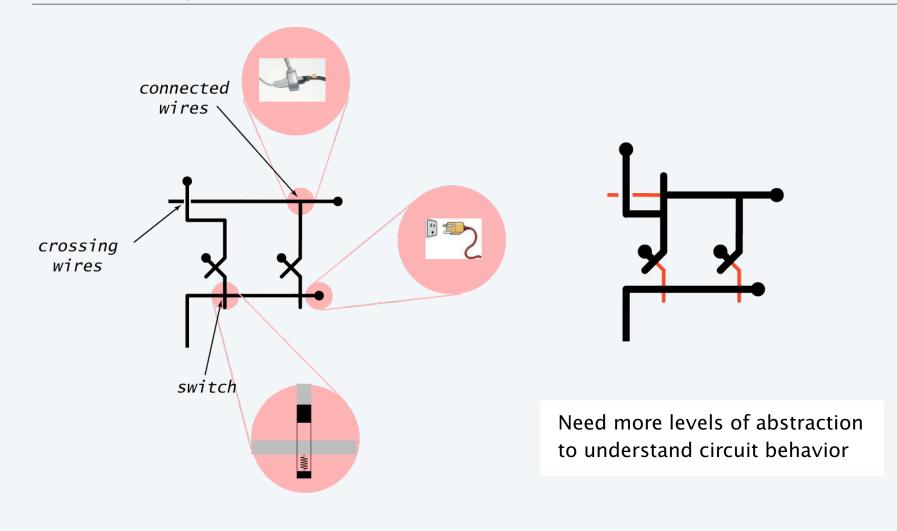

### Wires

### Wires propagate on/off values

- ON (1): connected to power.

- OFF (0): not connected to power.

- Any wire connected to a wire that is ON is also ON.

- Drawing convention: "flow" from top, left to bottom, right.

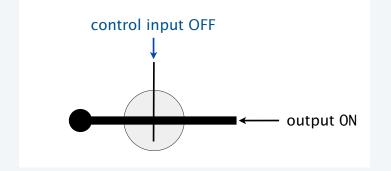

### **Controlled Switch**

### Switches control propagation of on/off values through wires.

- Simplest case involves two connections: control (input) and output.

- control OFF: output ON

- control ON: output OFF

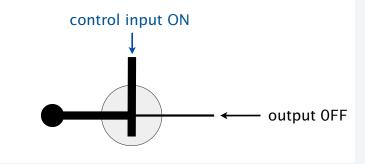

### **Controlled Switch**

### Switches control propagation of on/off values through wires.

- General case involves three connections: control input, data input and output.

- control OFF: output is connected to input

- control ON: output is disconnected from input

Idealized model of *pass transistors* found in real integrated circuits.

### Controlled switch: example implementation

A *relay* is a physical device that controls a switch with a magnet

- 3 connections: input, output, control.

- Magnetic force pulls on a contact that cuts electrical flow.

### First level of abstraction

Switches and wires model provides separation between physical world and logical world.

- We assume that switches operate as specified.

- That is the only assumption.

- Physical realization of switch is irrelevant to design.

Physical realization dictates performance

- Size.

- Speed.

- Power.

New technology immediately gives new computer.

Better switch? Better computer.

Basis of Moore's law.

all built with "switches and wires"

|            |                   |        | technology               | switch   |

|------------|-------------------|--------|--------------------------|----------|

| technology | "information"     | switch | relay                    | <b>A</b> |

|            |                   | A THE  | i cita y                 |          |

| pneumatic  | air pressure      |        | vacuum tube              |          |

| fluid      | water<br>pressure |        | transistor               |          |

|            |                   | -      | "pass transistor" in     |          |

| relay      | electric          |        | integrated circuit       |          |

|            | potential         |        | atom-thick<br>transistor |          |

|            | ing attempts t    |        |                          |          |

### Switches and wires: a first level of abstraction

scale but prove the point

**Real-world examples that prove the point**

### Switches and wires: a first level of abstraction

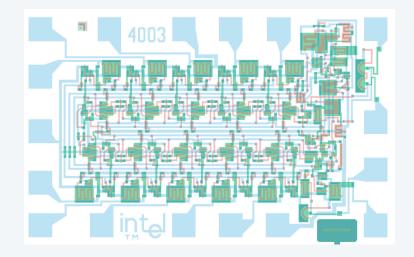

VLSI = Very Large Scale Integration

### Technology

Deposit materials on substrate.

### Key properties

Lines are wires. Certain crossing lines are controlled switches.

### Key challenge in physical world

Fabricating physical circuits with billions of wires and controlled switches

### Key challenge in "abstract" world

Understanding behavior of circuits with billions of wires and controlled switches

Bottom line. Circuit = Drawing (!)

### Circuit anatomy

### **COMPUTER SCIENCE** S E D G E W I C K / W A Y N E

### 20. Combinational Circuits

- Building blocks

- Boolean algebra

- Digital circuits

- Adder

CS.20.B.Circuits.Algebra

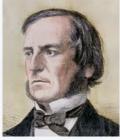

### Boolean algebra

Developed by George Boole in 1840s to study logic problems

• Variables represent *true* or *false* (1 or 0 for short).

• Basic operations are AND, OR, and NOT (see table below). Widely used in mathematics, logic and computer science.

George Boole 1815–1864

| operation | Java notation | logic notation | circuit design<br>(this lecture) |                                    |

|-----------|---------------|----------------|----------------------------------|------------------------------------|

| AND       | х && у        | $x \wedge y$   | xy                               |                                    |

| OR        | х    у        | $x \lor y$     | x + y                            | various notations<br>in common use |

| NOT       | ! x           | $\neg x$       | <i>x</i> '                       |                                    |

Example: (stay tuned for proof)

DeMorgan's Laws

$$(xy)' = (x' + y')$$

$$(x + y)' = x'y'$$

Relevance to circuits. Basis for next level of abstraction.

Copyright 2004, Sidney Harris http://www.sciencecartoonsplus.com

### Truth tables

A truth table is a systematic way to define a Boolean function

- One row for each possible set of argument values.

- Each row gives the function value for the specified argument values.

- *N* inputs: 2<sup>*N*</sup> rows needed.

| x | <i>x</i> ' |  | x   | У | xy | x  | y | x + y | X   | У | NOR | x   | У | ХО |

|---|------------|--|-----|---|----|----|---|-------|-----|---|-----|-----|---|----|

| 0 | 1          |  | 0   | 0 | 0  | 0  | 0 | 0     | 0   | 0 | 1   | 0   | 0 | 0  |

| 1 | 0          |  | 0   | 1 | 0  | 0  | 1 | 1     | 0   | 1 | 0   | 0   | 1 | 1  |

| N | ОТ         |  | 1   | 0 | 0  | 1  | 0 | 1     | 1   | 0 | 0   | 1   | 0 | 1  |

|   |            |  | 1   | 1 | 1  | 1  | 1 | 1     | 1   | 1 | 0   | 1   | 1 | 0  |

|   |            |  | AND |   |    | OR |   |       | NOR |   |     | XOR |   |    |

### Truth table proofs

### Truth tables are convenient for establishing identities in Boolean logic

- One row for each possibility.

- Identity established if columns match.

#### NOR NOR y' x' + y' $y \quad x+y \ (x+y)'$ *x*' y'x'y'xy (xy)'*x*' V X Y X X Y X (x + y)' = x'y' - $(xy)' = (x' + y') \checkmark$

#### **Proofs of DeMorgan's laws**

### All Boolean functions of two variables

- Q. How many Boolean functions of two variables?

- A. 16 (all possibilities for the 4 bits in the truth table column).

| x | У | ZERO | AND |   | x |   | У | XOR | OR | NOR | EQ | ¬y |   | ¬ <i>X</i> |   | NAND | ONE |

|---|---|------|-----|---|---|---|---|-----|----|-----|----|----|---|------------|---|------|-----|

| 0 | 0 | 0    | 0   | 0 | 0 | 0 | 0 | 0   | 0  | 1   | 1  | 1  | 1 | 1          | 1 | 1    | 1   |

| 0 | 1 | 0    | 0   | 0 | 0 | 1 | 1 | 1   | 1  | 0   | 0  | 0  | 0 | 1          | 1 | 1    | 1   |

| 1 | 0 | 0    | 0   | 1 | 1 | 0 | 0 | 1   | 1  | 0   | 0  | 1  | 1 | 0          | 0 | 1    | 1   |

| 1 | 1 | 0    | 1   | 0 | 1 | 0 | 1 | 0   | 1  | 0   | 1  | 0  | 1 | 0          | 1 | 0    | 1   |

#### Truth tables for all Boolean functions of 2 variables

### Functions of three and more variables

- Q. How many Boolean functions of *three* variables?

- A. 256 (all possibilities for the 8 bits in the truth table column).

| x | y | z | AND | OR | NOR | MAJ | ODD |

|---|---|---|-----|----|-----|-----|-----|

| 0 | 0 | 0 | 0   | 0  | 1   | 0   | 0   |

| 0 | 0 | 1 | 0   | 1  | 0   | 0   | 1   |

| 0 | 1 | 0 | 0   | 1  | 0   | 0   | 1   |

| 0 | 1 | 1 | 0   | 1  | 0   | 1   | 0   |

| 1 | 0 | 0 | 0   | 1  | 0   | 0   | 1   |

| 1 | 0 | 1 | 0   | 1  | 0   | 1   | 0   |

| 1 | 1 | 0 | 0   | 1  | 0   | 1   | 0   |

| 1 | 1 | 1 | 1   | 1  | 0   | 1   | 1   |

Some Boolean functions of 3 variables

|         |             | all extend to N variables                         |

|---------|-------------|---------------------------------------------------|

| Example | 25          | $\downarrow$                                      |

| AND     | logical AND | 0 iff <i>any</i> inputs is 0 (1 iff all inputs 1) |

| OR      | logical OR  | 1 iff any input is 1 (0 iff all inputs 0)         |

| NOR     | logical NOR | 0 iff <i>any</i> input is 1 (1 iff all inputs 0)  |

| MAJ     | majority    | 1 iff more inputs are 1 than 0                    |

| ODD     | odd parity  | 1 iff an odd number of inputs are 1               |

### Q. How many Boolean functions of *N* variables?

|                               | N | number of Boolean functions with N variables |

|-------------------------------|---|----------------------------------------------|

|                               | 2 | $2^4 = 16$                                   |

| △ 2 <sup>2</sup> <sup>N</sup> | 3 | 2 <sup>8</sup> = 256                         |

| A. 22                         | 4 | $2^{16} = 65,536$                            |

|                               | 5 | 2 <sup>32</sup> = 4,294,967,296              |

|                               | 6 | $2^{64} = 18,446,744,073,709,551,616$        |

17

### Universality of AND, OR and NOT

Every Boolean function can be represented as a sum of products

- Form an AND term for each 1 in Boolean function.

- OR all the terms together.

| 'z + xyz' + xyz = MA  | $v'v_7 \perp v_1$ |   |     |      |      |      |     |   |   |   |

|-----------------------|-------------------|---|-----|------|------|------|-----|---|---|---|

| 7 Z T XYZ T XYZ - MAJ | , ^ y Z +         | 1 | xyz | xyz' | xy'z | x'yz | MAJ | Ζ | У | X |

|                       |                   | 0 | 0   | 0    | 0    | 0    | 0   | 0 | 0 | 0 |

|                       |                   | 0 | 0   | 0    | 0    | 0    | 0   | 1 | 0 | 0 |

|                       |                   | 0 | 0   | 0    | 0    | 0    | 0   | 0 | 1 | 0 |

| Def. A set of op      |                   | 1 | 0   | 0    | 0    | 1    | 1   | 1 | 1 | 0 |

| every Boolean f       |                   | 0 | 0   | 0    | 0    | 0    | 0   | 0 | 0 | 1 |

| using just those      |                   | 1 | 0   | 0    | 1    | 0    | 1   | 1 | 0 | 1 |

| Fact. { AND, OR       |                   | 1 | 0   | 1    | 0    | 0    | 1   | 0 | 1 | 1 |

|                       |                   | 1 | 1   | 0    | 0    | 0    | 1   | 1 | 1 | 1 |

Expressing MAJ as a sum of products

Def. A set of operations is *universal* if every Boolean function can be expressed using just those operations.

Fact. { AND, OR, NOT } is universal.

### **COMPUTER SCIENCE** S E D G E W I C K / W A Y N E

### 20. Combinational Circuits

- Building blocks

- Boolean algebra

- Digital circuits

- Adder

CS.20.C.Circuits.Digital

### A basis for digital devices

### Claude Shannon connected circuit design with *boolean algebra* in 1937.

" Possibly the most important, and also the most famous, master's thesis of the [20th] century."

– Howard Gardner

### Key idea. Can use boolean algebra to systematically analyze circuit behavior.

| A Symbolic Anal<br>Switching                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | closed circuit, and the symbol 1 (unity) to<br>represent the hindrance of an open cir-<br>cuit. Thus when the circuit $a \cdot b$ is open<br>$X_{ab} = 1$ and when closed $X_{ab} = 0$ .<br>Two hindrances $X_{ab}$ and $X_{ab}$ will be<br>maid to be equal if whenever the circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| By CLAUDE E                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | a-b is open, the circuit $c-d$ is open, and<br>whenever $a-b$ is closed, $c-d$ is closed.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| I. Introduction<br>THE CONTROL and protective<br>circuits of complex electrical system<br>is frequently necessary to make in-<br>triate interconnections of relay contacts<br>and witches. Examples of these cir-<br>cuits occur in automatic telephone ex-<br>changes, industrial motor-control equip-<br>ment, and in almost any circuits designed<br>to perform complex operations auto-<br>matically. In this paper a mathematical<br>analysis of certain of the properties of<br>ancients will be given to the problem do<br>network synthesis. Given certain char-<br>asteristics, it is required to find a circuit<br>incorporating these characteristics. The<br>solution of this type of problem is not<br>using and methods of finding those par-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | bolics study of logic. For the synthesis<br>problem the desired characteristics and<br>first written as system of equations, and<br>the equations are then manipulated in<br>the form representing the simplest ci-<br>cuit. The circuit may then be immedi-<br>ately drawn from the equations. B<br>this method it is always possible to fin-<br>simplest circuit containing on<br>series and parallel connections, and i<br>come cases the simplest circuit containing<br>any type of connections.<br>Our notation is takenary system is<br>common use we have chosen the on-<br>which seems simplest and most suggestiv<br>for our interpretation. Some of our<br>phraseology, as node, mesh, delta, wyr<br>etc., is borrowed from ordinary network | and<br>end to together. Thus $X_{\alpha} + X_{\alpha}$ is the<br>hindrance of the circuit of when b and c<br>are connected together. Similarly the<br>product of two hindrances $X_{\alpha}X_{\alpha}$ or<br>more briefly $X_{\alpha}X_{\alpha}$ will be defined to<br>mean the hindrance of the circuit formed<br>by connecting the circuit so and so and<br>the properties of the source of the source<br>is a represented in a circuit by the weymal<br>is represented in hindrance ( nucleion King<br>2 shows the interpretation of the plus<br>agin and figure 3 the multiplication sign.<br>This choice of symbols makes the ma-<br>ingulation of hindrance struction. Figure<br>or dimary numerical algobra.<br>It is evident that with the above defi-<br>titions the following postulates will hold:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| icular circuits requiring the least num-<br>er of relay contacts and switch blades                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ostulates                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| will be studied. Methods will also be<br>described for finding any number of cir-<br>cuits equivalent to a given circuit in all<br>potenting characteristics. It will be<br>shown that several of the well-known<br>theorems on impedance networks have<br>roughly analogous theorems in relay<br>circuits. Notable among these are the<br>delta-syst and star-mesh transformations,<br>and the duality theorem.<br>The method of attack on these prob-<br>nems may be described briefly as follows:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | $ \begin{array}{c} circuit, \\ b. \ 1+1=1 \\ 2. \ a. \ 1+0=0+1=1 \\ b. \ 0\cdot1=1\cdot0=0 \\ 3. \ a. \ 0+0=0 \\ circuit, \\ \end{array} $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | circuit in parallel with a closed circuit is a closed<br>circuit in series with an open circuit is an open<br>circuit in series that a closed circuit in the there<br>$u_{i}$ , whether the open circuit is to the right or left<br>or closed circuit) as an open circuit in either<br>a closed circuit. In this closed circuit is a closed<br>circuit in series with a closed circuit is a closed<br>circuit in series with a closed circuit is a closed<br>circuit in grant circuit in a closed circuit is a closed<br>circuit in series with a closed circuit is a closed<br>circuit in series with a closed circuit is a closed<br>circuit in series with a closed circuit is a closed<br>circuit in grant circuit is closed circuit in circuit closed<br>circuit in closed circuit is closed circuit in closed circuit is closed<br>circuit in closed circuit closed circuit is closed circuit in closed circuit in closed circuit is closed circuit in closed circuit is closed circuit in closed circuit is closed circuit in closed circuit in closed circuit is closed circuit in closed circuit is closed circuit in closed circuit in closed circuit is closed circuit in closed circuit is closed circuit in closed circ |

| any circuit is represented by a set of<br>equations, the terms of the equations<br>corresponding to the various relays and<br>witches in the circuit. A calculus is<br>developed for manipulating these equa-<br>tions by simple mathematical processes,<br>most of which are similar to ordinary<br>algebraic algorisms. This calculus is<br>aboven to be exactly analogous to the<br>calculus of propositions used in the sym-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | theory for similar concepts in switchin<br>circuits.<br>II. Series-Parallel<br>Two-Terminal Circuits<br>FUNDAMENTAL DEFINITIONS<br>AND POSITIATES<br>We shall limit our treatment to ci-<br>cuits containing only relay contacts as                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | theorems which will be used in connection<br>with circuits containing only series and<br>parallel connections. The postulates are<br>arranged in pairs to emphasize a duality<br>relationship between the operations of<br>addition and multiplication and the<br>quantities zero and one. Thus, if in<br>ar- any of the a postulates the zero's are re-<br>d placed by one's and the multiplications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Paper manher M=06, recommended by the AIEE<br>committees or communication and bala existence<br>or committees or communication and bala existence<br>we prepare the second second second second second<br>balance of the second second second second second second<br>second second second second second second second second<br>communication of restances of the second second second<br>communication of restances of the second second second<br>second second second second second second second second second second second second second<br>second second s | switches, and therefore at any given in<br>the circuit between any two terminar<br>must be either open (infinite impedanco<br>or closed (zero impedance). Let us a<br>sociate a symbol $X_{ab}$ or more simply 2<br>with the terminals <i>a</i> and <i>b</i> . This var-<br>able, a (nuction of time, will be calle<br>the hindrance of the two-terminal <i>ci</i><br>cuit <i>a-b</i> . The symbol 0 (zero) will 1<br>used to represent the hindrance of                                                                                                                                                                                                                                                                                               | is responding b postulate will result. This<br>op fact is of great importance. It gives<br>as each theorem a dual theorem, it being<br>X, necessary to prove only one to establish<br>rish both. The only one of these postulates<br>a which differs from ordinary algebra is 1b.<br>fr. However, this enables great simplifica-<br>be tions in the manipulation of these                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 1938, Vol. 57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Shannon—Relay Circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 713                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

Claude Shannon 1916-2001

|          | I I   | ſ  | 1 1 1        | I •   |       |

|----------|-------|----|--------------|-------|-------|

| A second | level | ot | abstraction: | logic | qates |

|          |       |    |              | J     | J     |

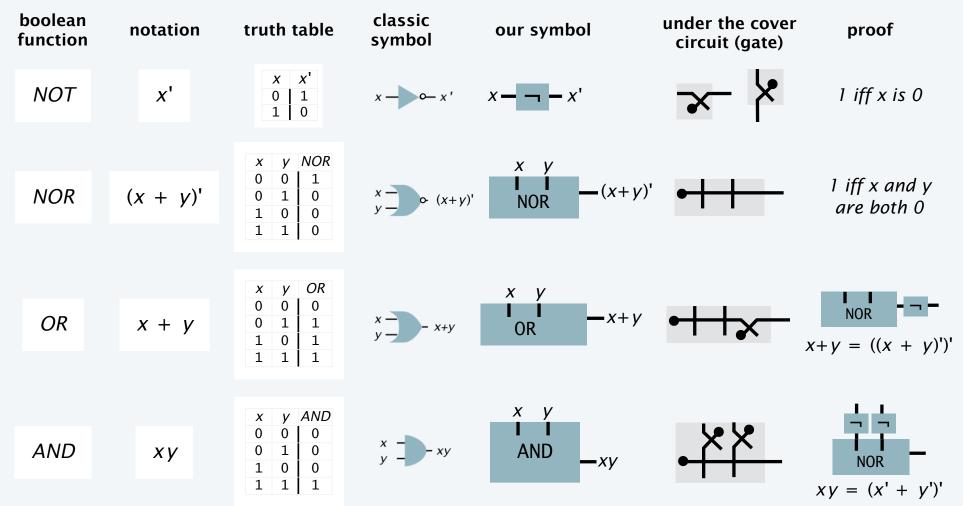

### Gates with arbitrarily many inputs

#### Multiway gates.

- OR: 1 if any input is 1; 0 if all inputs are 0.

- NOR: 0 if any input is 1; 1 if all inputs are 0.

- Generalized: Negate some inputs.

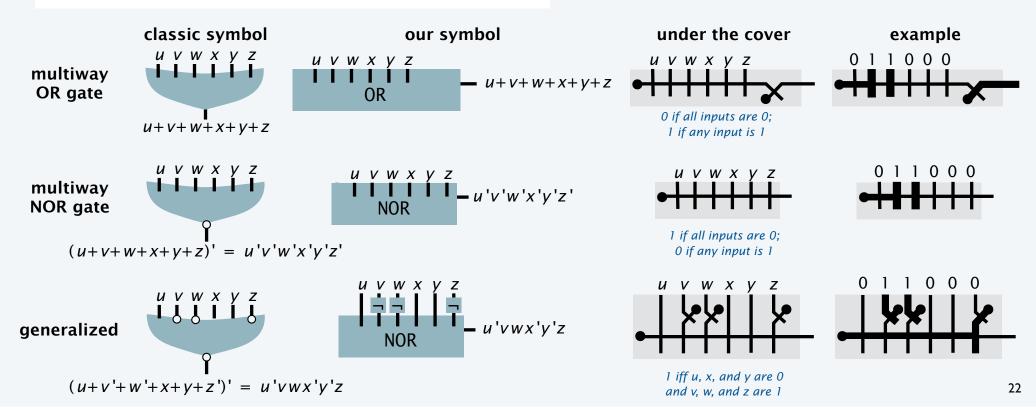

### Generalized NOR gate application: Decoder

## A *decoder* uses a binary address to switch on a single output line

- *n* address inputs, 2<sup>*n*</sup> outputs.

- Uses all 2<sup>n</sup> different generalized NOR gates.

- Addressed output line is 1; all others are 0.

| Y |   | - | <b>a</b> 0                          | a         | <b>a</b> 2 | <b>a</b> 3 | <b>a</b> 4 | <b>a</b> 5 | <b>a</b> 6 | <b>a</b> 7  |

|---|---|---|-------------------------------------|-----------|------------|------------|------------|------------|------------|-------------|

| X | У | Ζ | x'y'z'                              | x'y'z     | x'yz'      | x'yz       | xy'z'      | xy'z       | xyz'       | xyz         |

|   |   |   | ( <i>x</i> + <i>y</i> + <i>z</i> )' | (x+y+z')' | (x+y'+z)'  | (x+y'+z')' | (x'+y+z)'  | (x+y'+z)'  | (x'+y'+z)' | (x'+y'+z')' |

| 0 | 0 | 0 | 1                                   | 0         | 0          | 0          | 0          | 0          | 0          | 0           |

| 0 | 0 | 1 | 0                                   | 1         | 0          | 0          | 0          | 0          | 0          | 0           |

| 0 | 1 | 0 | 0                                   | 0         | 1          | 0          | 0          | 0          | 0          | 0           |

| 0 | 1 | 1 | 0                                   | 0         | 0          | 1          | 0          | 0          | 0          | 0           |

| 1 | 0 | 0 | 0                                   | 0         | 0          | 0          | 1          | 0          | 0          | 0           |

| 1 | 0 | 1 | 0                                   | 0         | 0          | 0          | 0          | 1          | 0          | 0           |

| 1 | 1 | 0 | 0                                   | 0         | 0          | 0          | 0          | 0          | 1          | 0           |

| 1 | 1 | 1 | 0                                   | 0         | 0          | 0          | 0          | 0          | 0          | 1           |

Next. Circuits for *any* boolean function.

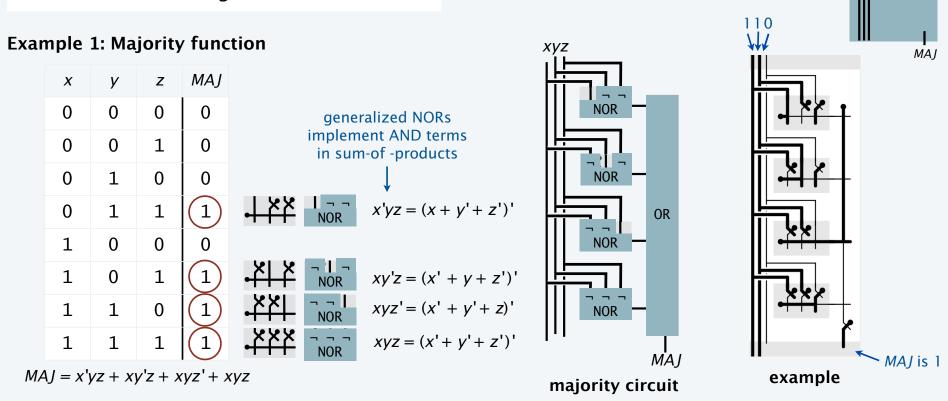

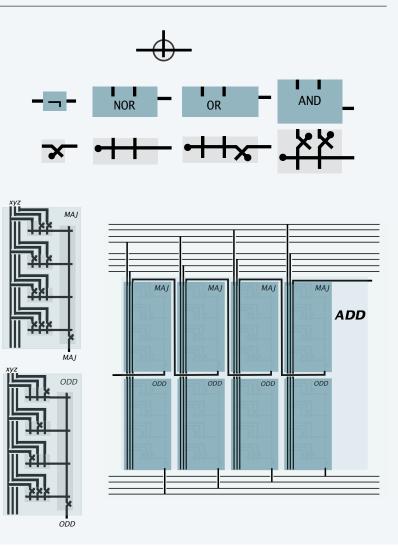

### Creating a digital circuit that computes a boolean function: majority

### Use the truth table

- Identify rows where the function is 1.

- Use a generalized NOR gate for each.

- OR the results together.

XVZ

### Creating a digital circuit that computes a boolean function: odd parity

### Use the truth table

- Identify rows where the function is 1.

- Use a generalized NOR gate for each.

- OR the results together.

XVZ

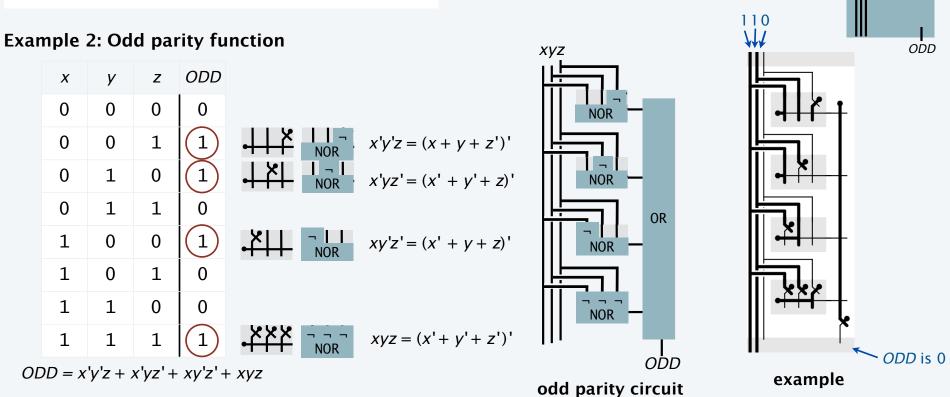

### Combinational circuit design: Summary

Problem: Design a circuit that computes a given boolean function.

### Ingredients

- OR gates.

- NOT gates.

- NOR gates.

- Wire.

### Method

- Step 1: Represent input and output with Boolean variables.

- Step 2: Construct truth table to define the function.

- Step 3: Identify rows where the function is 1.

- Step 4: Use a generalized NOR for each and OR the results.

Bottom line (profound idea): Yields a circuit for ANY function. Caveat (stay tuned): Circuit might be huge.

| x | У | z | MAJ | x | У | z | ODD |

|---|---|---|-----|---|---|---|-----|

| 0 | 0 | 0 | 0   | 0 | 0 | 0 | 0   |

| 0 | 0 | 1 | 0   | 0 | 0 | 1 |     |

| 0 | 1 | 0 | 0   | 0 | 1 | 0 |     |

| 0 | 1 | 1 |     | 0 | 1 | 1 | 0   |

| 1 | 0 | 0 | 0   | 1 | 0 | 0 |     |

| 1 | 0 | 1 |     | 1 | 0 | 1 | 0   |

| 1 | 1 | 0 |     | 1 | 1 | 0 | 0   |

| 1 | 1 | 1 | (1) | 1 | 1 | 1 | (1) |

### Self-assessment on combinational circuit design

Q. Design a circuit to implement XOR(x, y).

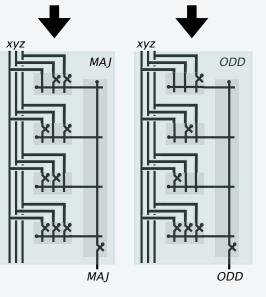

### Encapsulation

### Encapsulation in hardware design mirrors familiar principles in software design

- Building a circuit from wires and switches is the *implementation*.

- Define a circuit by its inputs and outputs is the API.

- We control complexity by *encapsulating* circuits as we do with ADTs.

### **COMPUTER SCIENCE** S E D G E W I C K / W A Y N E

### 20. Combinational Circuits

- Building blocks

- Boolean algebra

- Digital circuits

- Adder

CS.20.D.Circuits.Adder

30

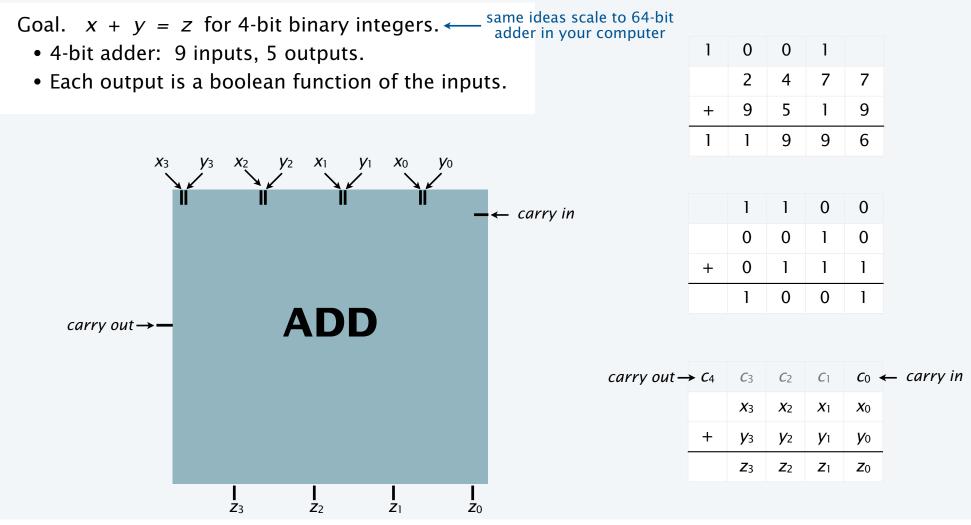

|                                       |                                                            |            |            |                    |            |            |            |            |            |            |            |            | <b>C</b> 4 | <b>C</b> 3 | <b>C</b> 2 | <b>C</b> 1 | <b>C</b> 0         |           |    |

|---------------------------------------|------------------------------------------------------------|------------|------------|--------------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|--------------------|-----------|----|

| Goal: $x + y = z$ for 4-bit integers. |                                                            |            |            |                    |            |            |            |            | <b>X</b> 3 | <b>X</b> 2 | <i>X</i> 1 | <b>X</b> 0 |            |            |            |            |                    |           |    |

| Strawman solu                         | Strawman solution: Build truth tables for each output bit. |            |            |                    |            |            |            |            | +          | <b>y</b> 3 | <b>y</b> 2 | <b>y</b> 1 | <b>y</b> 0 |            |            |            |                    |           |    |

|                                       |                                                            |            |            |                    |            |            |            | : - [      |            | -          |            |            |            | <b>Z</b> 3 | <b>Z</b> 2 | <b>Z</b> 1 | <b>Z</b> 0         |           |    |

|                                       |                                                            |            |            |                    |            |            |            |            |            |            |            |            |            |            |            |            |                    |           |    |

|                                       | <b>C</b> 0                                                 | <b>X</b> 3 | <b>X</b> 2 | $\boldsymbol{X}_1$ | <b>X</b> 0 | <b>y</b> 3 | <b>y</b> 2 | <b>y</b> 1 | <b>y</b> 0 | <b>C</b> 4 | <b>Z</b> 3 | <b>Z</b> 2 | <b>Z</b> 1 | <b>Z</b> 0 |            |            |                    |           |    |

|                                       | 0                                                          | 0          | 0          | 0                  | 0          | 0          | 0          | 0          | 0          | 0          | 0          | 0          | 0          | 0          | ĸ          |            |                    |           |    |

|                                       | 0                                                          | 0          | 0          | 0                  | 0          | 0          | 0          | 0          | 1          | 0          | 0          | 0          | 0          | 1          |            |            |                    |           |    |

| 4-bit adder<br>truth table            | 0                                                          | 0          | 0          | 0                  | 0          | 0          | 0          | 1          | 0          | 0          | 0          | 0          | 1          | 0          |            |            |                    |           |    |

|                                       | 0                                                          | 0          | 0          | 0                  | 0          | 0          | 0          | 1          | 1          | 0          | 0          | 0          | 1          | 1          | -          |            | 2 <sup>8+1</sup> = | = 512 row | s! |

|                                       |                                                            |            |            |                    |            |            |            |            |            |            |            |            |            |            |            | /          |                    |           |    |

|                                       | 1                                                          | 1          | 1          | 1                  | 1          | 1          | 1          | 1          | 0          | 1          | 1          | 1          | 1          | 0          |            |            |                    |           |    |

|                                       | 1                                                          | 1          | 1          | 1                  | 1          | 1          | 1          | 1          | 1          | 1          | 1          | 1          | 1          | 1          |            |            |                    |           |    |

Q. Why is this a bad idea?

A. 128-bit adder:  $2^{256+1}$  rows >> # electrons in universe!

| Goal: $x + y = z$ for 4-bit integers. |  |

|---------------------------------------|--|

|---------------------------------------|--|

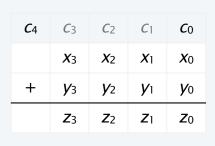

### Do one bit at a time.

- Build truth table for carry bit.

- Build truth table for sum bit.

|           | Xi | <b>y</b> i | Ci | <b>C</b> i+1 | MAJ |

|-----------|----|------------|----|--------------|-----|

|           | 0  | 0          | 0  | 0            | 0   |

|           | 0  | 0          | 1  | 0            | 0   |

|           | 0  | 1          | 0  | 0            | 0   |

| carry bit | 0  | 1          | 1  | 1            | 1   |

|           | 1  | 0          | 0  | 0            | 0   |

|           | 1  | 0          | 1  | 1            | 1   |

|           | 1  | 1          | 0  | 1            | 1   |

|           | 1  | 1          | 1  | 1            | 1   |

| A | surp | rise! |

|---|------|-------|

|---|------|-------|

- Carry bit is MAJ.

- Sum bit is ODD.

| <b>C</b> 4 | <b>C</b> 3 | <b>C</b> 2 | <b>C</b> 1 | <b>C</b> 0 |

|------------|------------|------------|------------|------------|

|            | <b>X</b> 3 | <b>X</b> 2 | <b>X</b> 1 | <b>X</b> 0 |

| +          | <b>y</b> 3 | <b>y</b> 2 | <b>y</b> 1 | <b>y</b> 0 |

|            | <b>Z</b> 3 | <b>Z</b> 2 | <b>Z</b> 1 | <b>Z</b> 0 |

|         | Xi | <b>y</b> i | Ci | Zi | ODD |

|---------|----|------------|----|----|-----|

|         | 0  | 0          | 0  | 0  | 0   |

|         | 0  | 0          | 1  | 1  | 1   |

|         | 0  | 1          | 0  | 1  | 1   |

| sum bit | 0  | 1          | 1  | 0  | 0   |

|         | 1  | 0          | 0  | 1  | 1   |

|         | 1  | 0          | 1  | 0  | 0   |

|         | 1  | 1          | 0  | 0  | 0   |

|         | 1  | 1          | 1  | 1  | 1   |

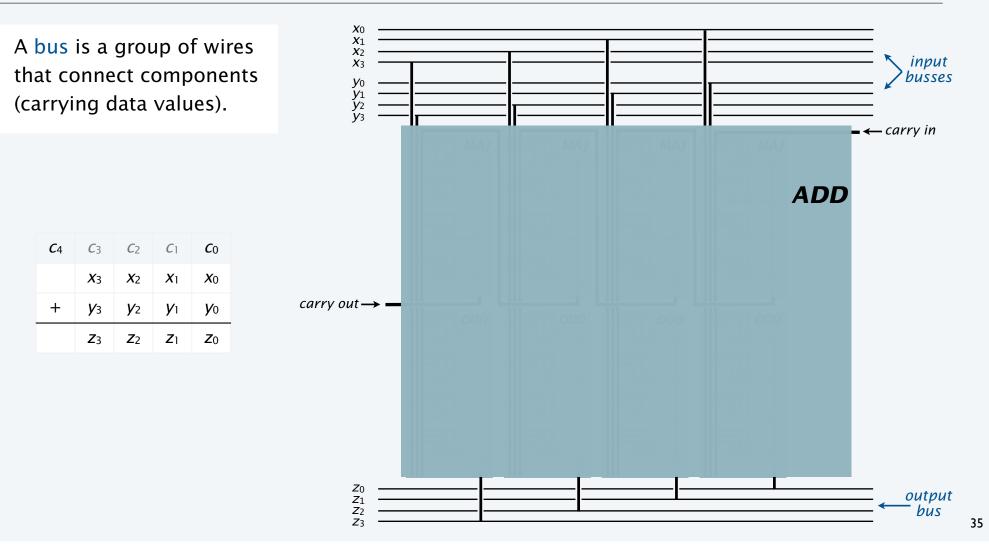

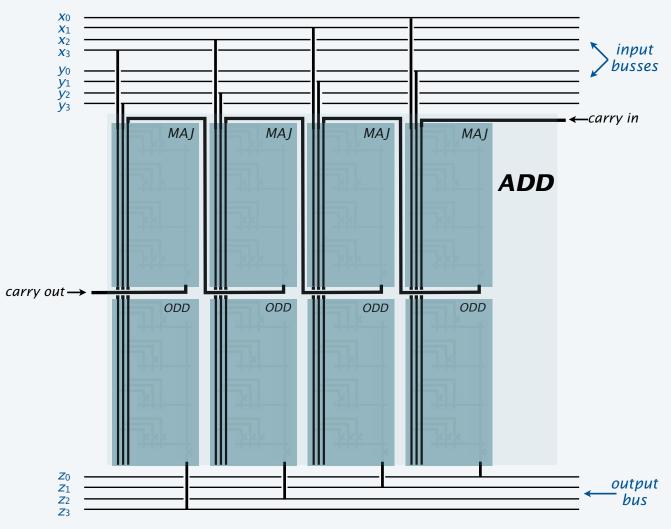

Goal: x + y = z for 4-bit integers.

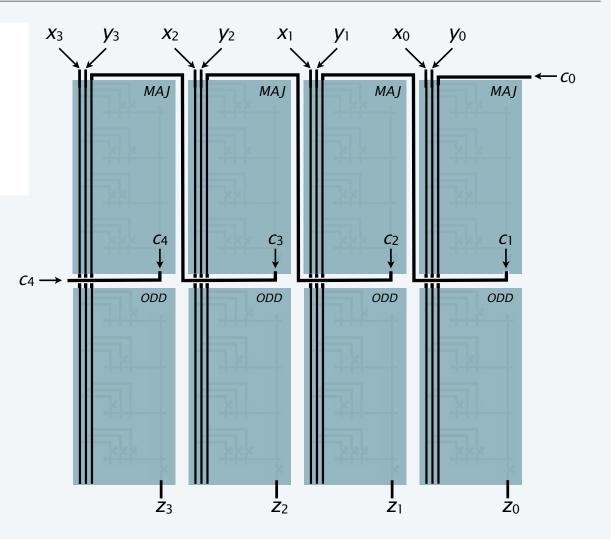

### Do one bit at a time.

- Use MAJ and ODD circuits.

- Chain together 1-bit adders to "ripple" carries.

### Adder interface (4-bit)

Adder component-level view (4-bit)

| <b>C</b> 4 | <b>C</b> 3 | С2         | <b>C</b> 1 | <b>C</b> 0 |

|------------|------------|------------|------------|------------|

|            | <b>X</b> 3 | <b>X</b> 2 | <b>X</b> 1 | <b>X</b> 0 |

| +          | <b>y</b> 3 | <b>y</b> 2 | <b>y</b> 1 | <b>y</b> 0 |

|            | <b>Z</b> 3 | <b>Z</b> 2 | <b>Z</b> 1 | <b>Z</b> 0 |

36

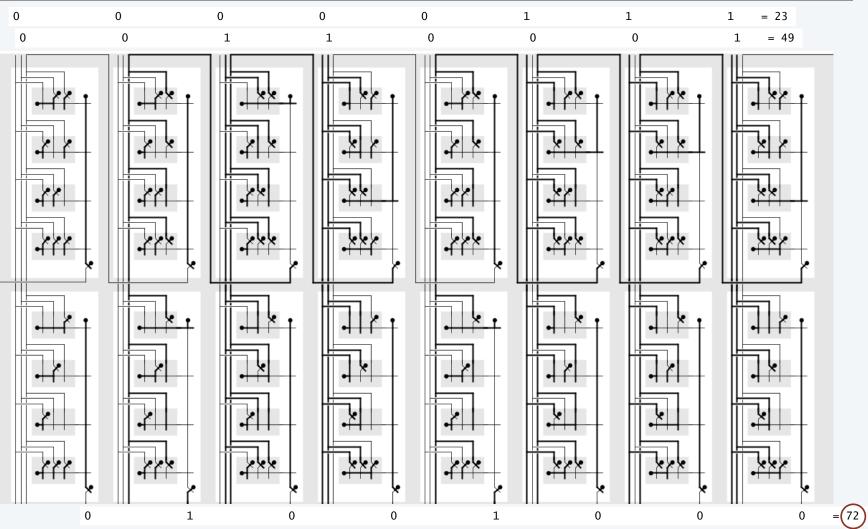

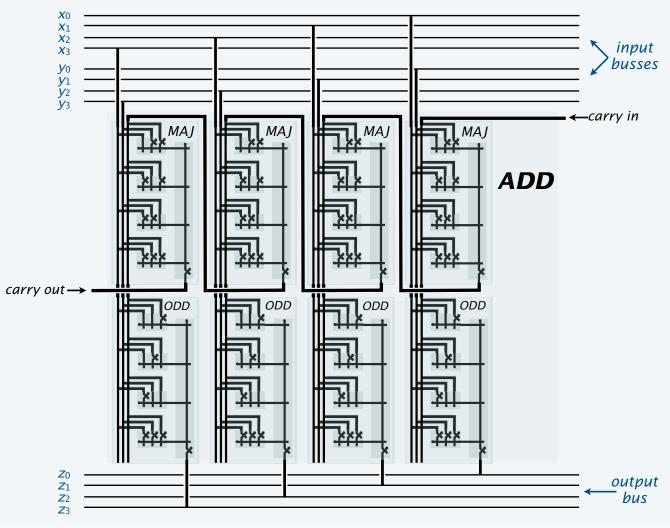

### Adder switch-level view (4-bit)

| <b>C</b> 4 | <b>C</b> 3 | <b>C</b> <sub>2</sub> | <b>C</b> 1 | <b>C</b> 0 |

|------------|------------|-----------------------|------------|------------|

|            | <b>X</b> 3 | <b>X</b> 2            | <b>X</b> 1 | <b>X</b> 0 |

| +          | <b>y</b> 3 | <b>y</b> 2            | <b>y</b> 1 | <b>y</b> 0 |

|            | <b>Z</b> 3 | <b>Z</b> 2            | <b>Z</b> 1 | <b>Z</b> 0 |

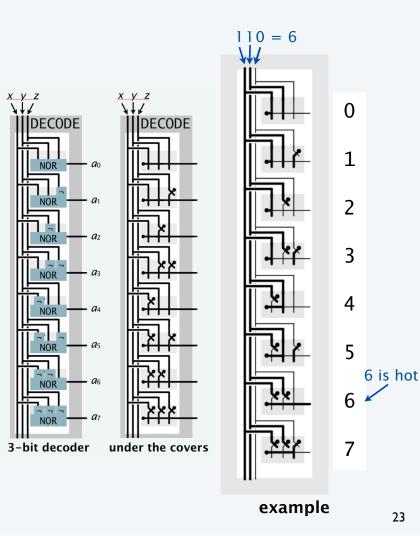

### Summary

Lessons for software design apply to hardware!

- Interface describes behavior of circuit.

- Implementation gives details of how to build it.

- Boolean logic gives understanding of behavior.

Layers of abstraction apply with a vengeance!

- On/off.

- Controlled switch. [relay, pass transistor]

- Gates. [NOT, NOR, OR, AND]

- Boolean functions. [MAJ, ODD]

- Adder.

- ...

- Arithmetic/Logic unit (ALU).

- ...

- TOY machine (stay tuned).

- Your computer.

**COMPUTER SCIENCE** S E D G E W I C K / W A Y N E

# COMPUTER SCIENCE

An Interdisciplinary Approach

ROBERT SEDGEWICK KEVIN WAYNE

http://introcs.cs.princeton.edu

# **20.** Combinational Circuits