### An Overview of Computer Architecture

CS 217

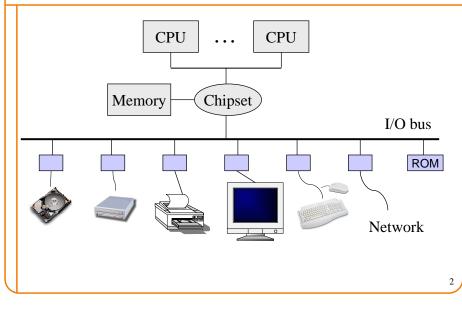

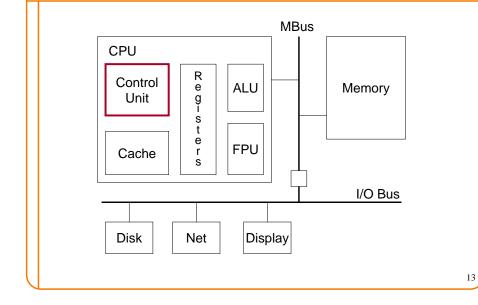

# **A Typical Computer**

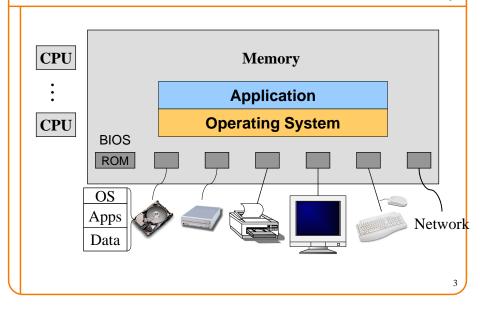

# A Typical Computer System

# **OS Service Examples**

- · Examples that are not provided at user level

- System calls: file open, close, read and write

- Control the CPU so that users won't get stuck by running – while (1);

- Protection:

- Keep user programs from crashing OS

- Keep user programs from crashing each other

- Examples that can be provided at user level

- $\circ~$  Read time of the day

#### **Processor Management**

- · Goals

- Overlap between I/O and computation

- Time sharing

- Multiple CPU allocations

- Issues

- Do not waste CPU resources

- Synchronization and mutual exclusion

- Fairness and deadlock free

# **Processor Management**

#### time

CPU

CPU

I/O

- Goals

- Overlap between I/O and computation

- Time sharing

- Multiple CPU allocations

- Issues

- Do not waste CPU resources

- Synchronization and mutual exclusion

- Fairness and deadlock free

#### **Processor Management**

time

CPU

CPU

CPU

I/O

CPU

I/O

5

- · Goals

- Overlap between I/O and computation

- Time sharing

- Multiple CPU allocations

- Issues

- Do not waste CPU resources

- Synchronization and mutual exclusion

- Fairness and deadlock free

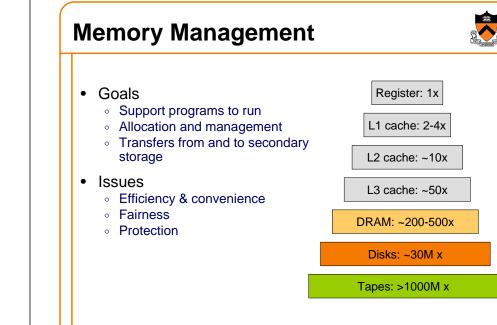

#### **Memory Management**

9

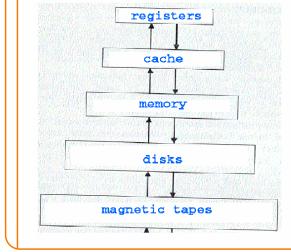

#### **Storage Hierarchies**

# Each lower level is slower, - bigger, Who manages what

- farther away, and

- cheaper

- registers: compiler

- cache: hardware

- memory: OS - disk: OS

- The performance of lower level is becoming increasingly important

## **Memory Management**

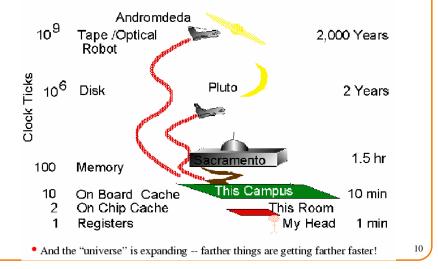

#### Storage Hierarchy Latency (by Jim Gray)

#### **General Computer Architecture**

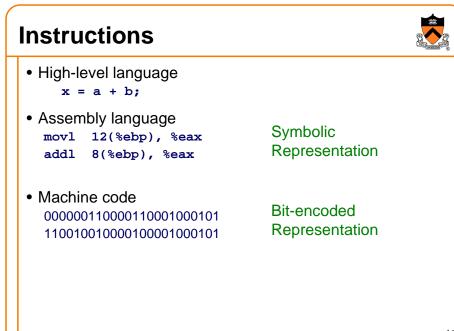

### **General Instruction Execution**

CPU's control unit executes a program PC ← memory location of first instruction while (PC != last\_instr\_addr) { i = fetch(MEM[PC++]); execute(i);

}

• Multiple phases...

- Fetch: instruction fetch; increment PC

- Execute: arithmetic instructions, compute branch target address, compute memory addresses

- Memory access: read/write memory

- Store: write results to registers

| Fetch | Execute | Memory | Store | Fetch | Execute | Memory | Store |    |

|-------|---------|--------|-------|-------|---------|--------|-------|----|

|       |         |        |       |       |         |        |       | 14 |

# **Concept of Instruction Pipelining**

• A simple pipeline

Fetch

Execute

Memory

Store

Fetch

Execute

Memory

Store

Fetch

Execute

Memory

Store

- What about branch instruction?

- Modern CPUs usually have deep pipelines

- $\circ~$  Pentium II has a 10-stage pipeline

- Pentium 4 has a 20-stage pipeline

- They all have sophisticated branch prediction mechanisms

foo.c

bar.c

- IA32 has variable-sized instructions

- Example:

push %ebp

mov %esp,%ebp

0x8B 0xE589

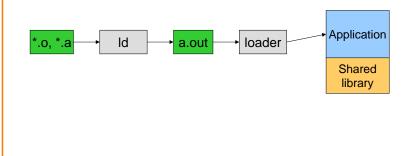

# **Execution (Run An Application)**

17

19

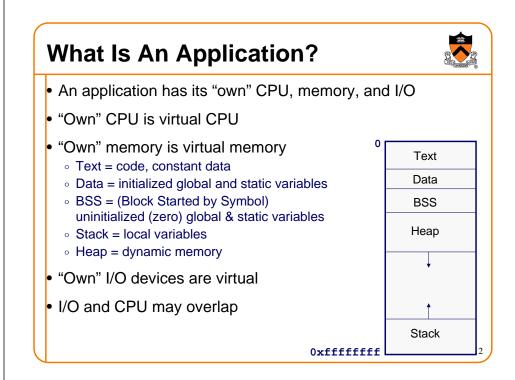

- On Unix, "loader" does the job

- Read an executable file

- Layout the code, data, heap and stack

- Dynamically link to shared libraries

- Prepare for the OS kernel to run the application

• Compiler part of gcc compiles a program into assembly

Pipeline of Creating An Executable File 💑

as

as

foo.o

bar.o

libc.a

ld

a.out

18

- Assembler compiles assembly code into relocatable object file

- · Linker links object files into an executable

• gcc can compile, assemble, and link together

foo.s

bar.s

gcc

gcc

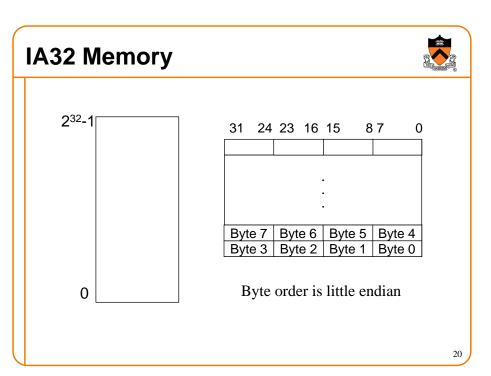

### **IA32 Architecture Registers**

| 31                   | 15 8        | 37      | _  |     | 15         | 0        |

|----------------------|-------------|---------|----|-----|------------|----------|

|                      | AH          | AL      | AX | EAX |            | CS       |

|                      | BH          | BL      | BX | EBX |            | DS       |

|                      | CH          | CL      | СХ | ECX |            | SS       |

|                      | DH          | DL      | DX | EDX |            | ES       |

|                      | E           | 3P      |    | EBP |            | FS       |

|                      |             | SI      |    | ESI |            | GS       |

|                      |             | DI      |    | EDI | Segment re |          |

|                      | 5           | SP      |    | ESP | Segment N  | egisters |

| General-             | purpose reg | gisters |    |     |            |          |

|                      |             |         | _  |     |            |          |

| FFL                  | AGS registe | ۰r      |    |     |            |          |

| EFLA                 | AGS registe | er      |    |     |            |          |

| EFLA<br>EIP (Instrue |             |         |    |     |            |          |

#### **Upcoming Lectures ...**

- Mode, registers and addressing

- Arithmetic and logic Instructions

- Control transfer instructions

- Assembly directives

- Assembler

**Revisit IA32 General Registers**

- 8 32-bit general-purpose registers (e.g. EAX)

- Each lower-half can be addressed as a 16-bit register (e.g. AX)

- Each 16-bit register can be addressed as two 8-bit registers (e.g AH and HL)

| 31 | 16 | 15 8 | 37 0 |

|----|----|------|------|

|    |    | AH   | AL   |

|    |    | BH   | BL   |

|    |    | СН   | CL   |

|    |    | DH   | DL   |

|    |    | SI   |      |

|    |    |      | DI   |

|    |    |      | 3P   |

|    | SP |      |      |

- AX EAX: Accumulator for operands, results

- BX EBX: Pointer to data in the DS segment.

- CX ECX: Counter for string, loop operations. DX EDX: I/O pointer.

ESI: Pointer to DS data, string source EDI: Pointer to ES data, string destination EBP: Pointer to data on the stack ESP: Stack pointer (in the SS segment)

# **EIP Register**

22

- Instruction Pointer or "Program Counter"

- Software change it by using

- Unconditional jump

- Conditional jump

- Procedure call

- Return

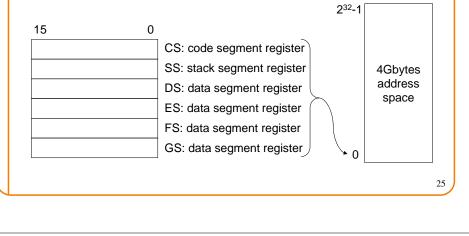

# **Segment Registers**

- IA32 memory is divided into segments, pointed by segment registers

- Modern operating system and applications use the (unsegmented) memory mode: all the segment registers are loaded with the same segment selector so that all memory references a program makes are to a single linear-address space.