## **Condition Codes**

• processor state register (psr)

|    | mpl | ver | icc |    | EC | E<br>F |    | S | P<br>S | E<br>T | CWP |  |

|----|-----|-----|-----|----|----|--------|----|---|--------|--------|-----|--|

| 31 |     | 27  | 23  | 19 | 13 | 12     | 11 | 7 | 6      | 5      | 4   |  |

• integer condition codes — the *icc* field — holds 4 bits

| Ν  | Ζ  | V  | С  |

|----|----|----|----|

| 23 | 22 | 21 | 20 |

- **N** set if the last ALU result was <u>n</u>egative

- **Z** set if the last ALU result was <u>zero</u>

- V set if the last ALU result overflowed

- C set if the last ALU instruction that modified *icc* caused a <u>carry out of</u>, or a borrow into, bit 31

- cc versions of the integer arithmetic instructions set all the codes

- cc versions of the logical instructions set only N and Z

- tests on the condition codes implement conditionals and loops

- carry and overflow are used to implement multiple-precision arithmetic

- see page 28 in the SPARC Architecture Manual, §4.8 in Paul

- test and compare *synthetic* instructions set condition codes

- to test a single value

tst reg orcc reg,%g0,%g0

compare two values

| cmp | $\textit{src}_1$ , $\textit{src}_2$ | subcc | $\mathit{src}_1$ , $\mathit{src}_2$ , %g0 |

|-----|-------------------------------------|-------|-------------------------------------------|

| cmp | src , value                         | subcc | <i>src</i> , <i>value</i> ,%g0            |

• using %g0 as a destination discards the result

• if the carry bit (*c*) is set

the last addition resulted in a carry

or the last subtraction resulted in a borrow

carry is needed to implement arithmetic using numbers represented in several words, e.g. multiple-precision addition

```

addcc %g3,%g5,%g7

addxcc %g2,%g4,%g6

(%g6,%g7) = (%g2,%g3) + (%g4,%g5)

the most-significant word is in the even register;

the least-significant word is in the odd register

```

overflow (V) indicates that the result of signed addition or subtraction doesn't fit

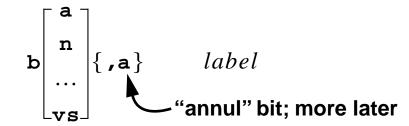

### **Branches**

• branch instructions transfer control based on *icc*

branches are format 2 instructions

- target is a <u>*PC-relative*</u> address and is  $PC + 4 \times disp22$ , where PC is the address of the branch instruction

- unconditional branches

| branch | condition     | synthetic<br>synonym |

|--------|---------------|----------------------|

| ba     | branch always | jmp                  |

| bn     | branch never  | nop                  |

## Branches, cont'd

• raw condition-code branches

| branch | condition  | synthetic<br>synonym |

|--------|------------|----------------------|

| bnz    | ! <i>Z</i> |                      |

| bz     | Ζ          |                      |

| bpos   | ! <b>N</b> |                      |

| bneg   | Ν          |                      |

| bcc    | ! <b>C</b> | bgeu                 |

| bcs    | С          | blu                  |

| bvc    | ! V        |                      |

| bvs    | V          |                      |

• comparisons

| branches | signed                    | unsigned                 | synthetic<br>synonym |

|----------|---------------------------|--------------------------|----------------------|

| be       | Ζ                         | Ζ                        | bz                   |

| bne      | ! <b>Z</b>                | ! <i>Z</i>               | bnz                  |

| bg bgu   | !(Z   (N^V))              | !( <b>C</b>   <b>Z</b> ) |                      |

| ble bleu | Z   (N^V)                 | C   Z                    |                      |

| bge bgeu | ! ( <i>N</i> ^ <i>V</i> ) | ! <b>C</b>               |                      |

| bl blu   | N^ V                      | С                        |                      |

- normally, instructions are fetched and executed from sequential memory locations

- program counter, *PC*, is address of the current instruction, and the program counter, *nPC*, is address of the next instruction: nPC = PC + 4

- branches, control-transfer instructions change *nPC* to something else

- control-transfer instructions

| instruction          | type                    | addressing mode                                |

|----------------------|-------------------------|------------------------------------------------|

| b <i>icc</i>         | conditional branches    | <i>PC</i> -relative                            |

| fb <b>fcc</b>        | floating point          | <i>PC</i> -relative                            |

| cb <b>ccc</b>        | coprocessor             | <i>PC</i> -relative                            |

| jmpl                 | jump and link           | register indirect                              |

| rett                 | return from trap        | register indirect                              |

| call<br>t <i>icc</i> | procedure call<br>traps | <b>PC</b> -relative register-indirect vectored |

• *PC*-relative addressing is like register displacement addressing that uses *PC* as the base register

# **Control Transfer, cont'd**

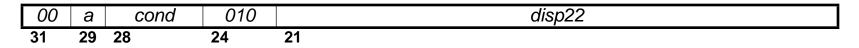

#### • branches

| 00 | а  | cond | 010 | disp22 |

|----|----|------|-----|--------|

| 31 | 29 | 28   | 24  | 21     |

$nPC = PC + 4 \times signestend(disp22)$

jumping to an arbitrary location may require two branches, but branches are used to build conditionals and loops in "small" code blocks

#### • calls

| 01 | disp30 |  |

|----|--------|--|

| 31 | 29     |  |

$nPC = PC + 4 \times \text{zeroextend}(disp30)$

is multiplied by 4 because all instructions are word aligned

<u>position-independent</u> code is code whose correct execution does not depend on where it is loaded, i.e., all instructions use *PC*-relative addressing

# **Branching Examples**

#### • if-then-else

```

if (a > b)

c = a;

else

c = b;

becomes

#define a %10

#define b %11

#define c %13

cmp a,b

ble L1; nop

mov a,c

ba L2; nop

L1: mov b,c

L2: ...

```

### loops

```

for (i = 0; i < n; i++)

....

becomes

#define i %10

#define n %11

L1: cmp i,n

bge L2; nop

...

inc i

ba L1; nop

L2:</pre>

```

#### • lcc generates

```

clr i

ba L5; nop

L2: ...

inc i

L5: cmp i,n

bl L2; nop

```