# Sequential circuits

- Q. What is a sequential circuit?

- A. A digital circuit (all signals are 0 or 1) with feedback (loops).

- Q. Why sequential circuits?

- A. Memory (difference between a DFA and a Turing machine).

### Basic abstractions

- On and off.

- Wire: Propagates an on/off value.

- Switch: Controls propagation of on/off values through wires.

- Flip-flop: Remembers a value.

# Simple circuits with feedback

# Loops in circuits lead to time-varying behavior

- Sequence of switch operation matters.

- Need tight control (see next slide).

Example 1. Two switches, each blocked by the other.

- State determined by whichever switches first.

- Stable (once set, state never changes).

- Basic building block for memory circuits.

Example 2. Three switches, blocked in a cycle.

- State determined by whichever switches first.

- Not stable (cycles through states).

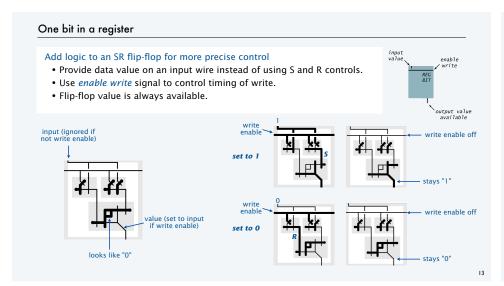

# A new ingredient: Circuits with memory An SR flip-flop controls feedback. • Add control lines to switches in simple feedback loop. • R (reset) sets state to 0. • S (set) sets state to 1. • Q (state) is always available. S: set to 1 output value (state) S: set to 1 output value (state) Caveat. Timing of switch vs. propagation delay.

11

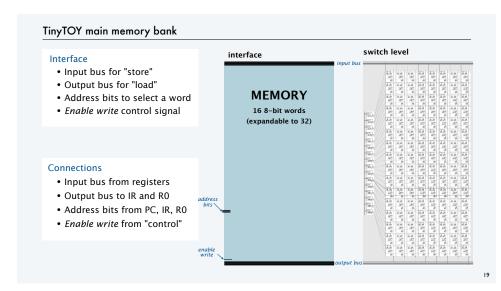

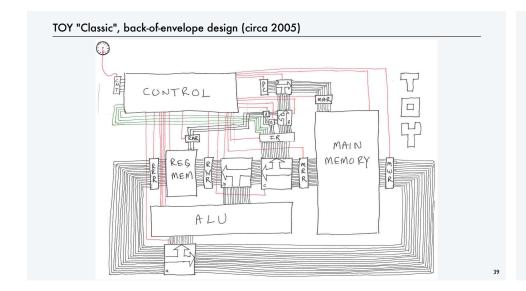

# Designing a digital circuit: overview Steps to design a digital (sequential) circuit

- Design interface: input busses, output busses, control signals.

- Determine components.

- Determine datapath requirements: "flow" of bits.

- Establish control sequence.

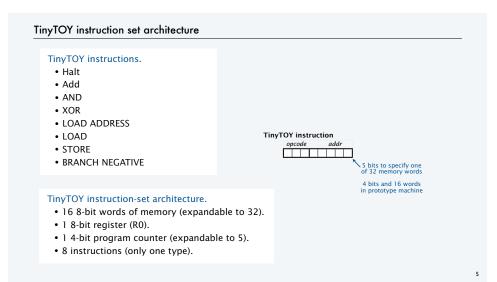

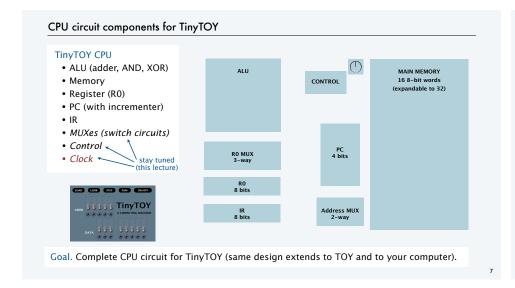

Another useful combinational circuit: Multiplexer 3-WAY BUS MUX (4-bit) Bus multiplexer (MUX). • Combinational circuit to select among input buses. • Exactly one select line i is activated. • Puts bit values from input bus i onto output bus. Note: MUX in text takes binary select specification example output is value of Typical use. Connect a component in different ways at different times.

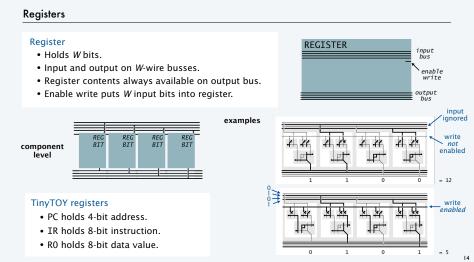

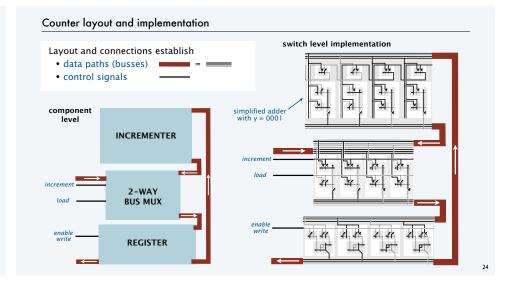

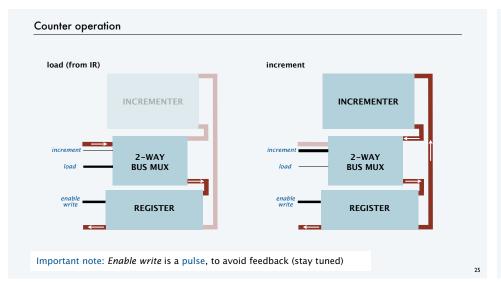

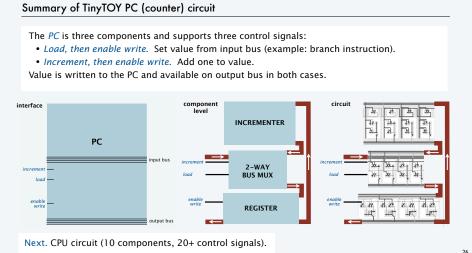

# Counter interface A Counter holds a value and supports 3 control signals: • Increment. Add 1 to value. • Load. Set value from input bus. • Enable write. Make value available on output bus. Components inside **COUNTER** • Register. • Incrementer (add 1). input bus increment • 2-way MUX. load TinyTOY PC: 4-bit counter 23

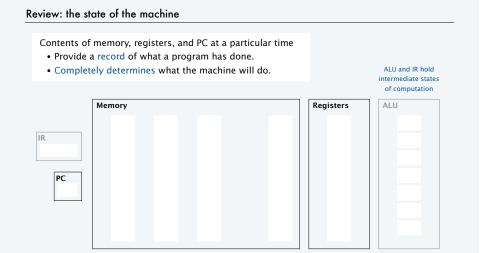

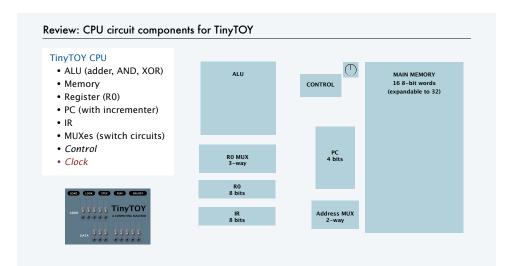

Review: Program counter and instruction register

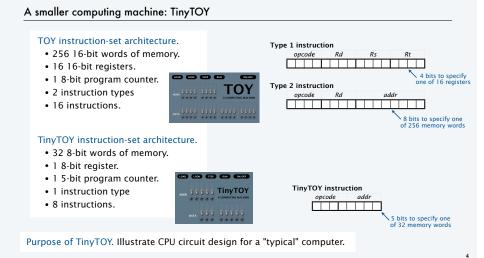

TOY operates by executing a sequence of instructions.

# Critical abstractions in making this happen

- Program Counter (PC). Memory address of next instruction.

- Instruction Register (IR). Instruction being executed.

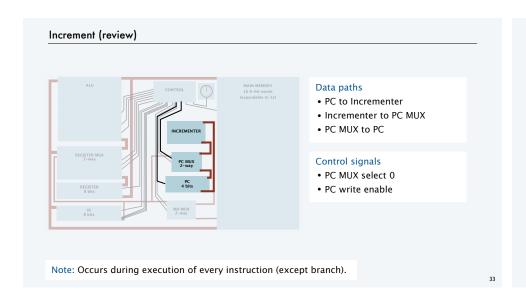

## Fetch-increment-execute cycle

- Fetch: Get instruction from memory into IR.

- Increment: Update PC to point to next instruction.

- Execute: Move data to or from memory, change PC, or perform calculations, as specified by IR.

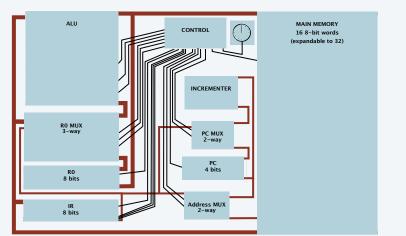

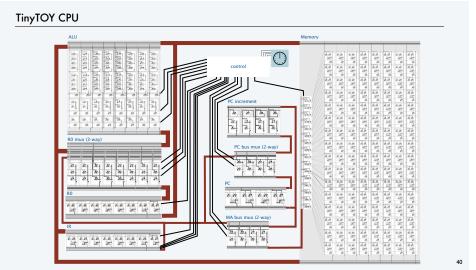

# TinyToy data paths and control lines

# Fetch (every instruction)

29

# Data paths

- PC to Address MUX

- Address MUX to memory

- · Memory to IR

# Control signals

- Address MUX select 1

- IR Write Enable

32

# Add instruction

# Data paths

- IR to Address MUX

- Address MUX to memory

- Memory to ALU

- R0 to ALU

- ALU to R0 MUX

- R0 MUX to R0

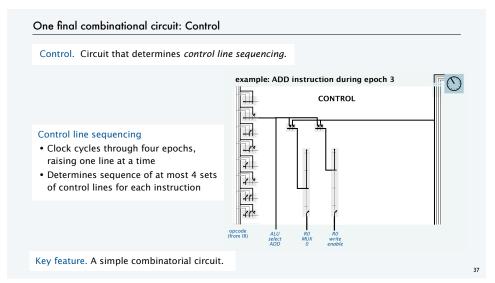

# Control signals

- ALU Select ADD

- Address MUX select 0

- R0 MUX Select 0

- R0 Write Enable

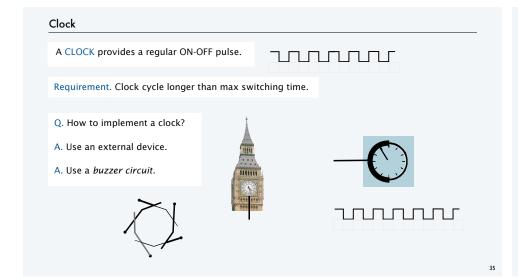

Two-cycle design. Each control signal is in one of four epochs.

| epoch | name          | example             |

|-------|---------------|---------------------|

| 0     | fetch         | set MA from PC      |

| 1     | fetch/write   | load IR from memory |

| 2     | execute       | set ALU inputs      |

| 3     | execute/write | load R0 from ALU    |

0 1 2

Key feature. A sequence of signals.

36

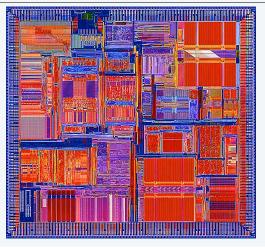

# A real microprocessor (MIPS R10000)

H