http://xkcd.com/730/

### Programming in Java

Robert Sedgewick • Kevin Wayne

An Interdisciplinary Approach

Sections 6.2 and 6.3

http://introcs.cs.princeton.edu

## **21. Central Processing Unit**

#### Let's build a computer!

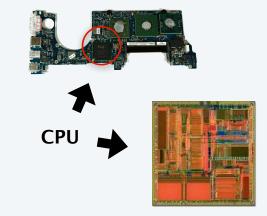

CPU = Central Processing Unit

#### Computer

Display Touchpad Battery Keyboard

•••

CPU (difference between a TV set and a computer)

#### **Previous lecture**

Combinational circuits ALU (calculator)

#### This lecture

Sequential circuits with *memory* CPU (computer)

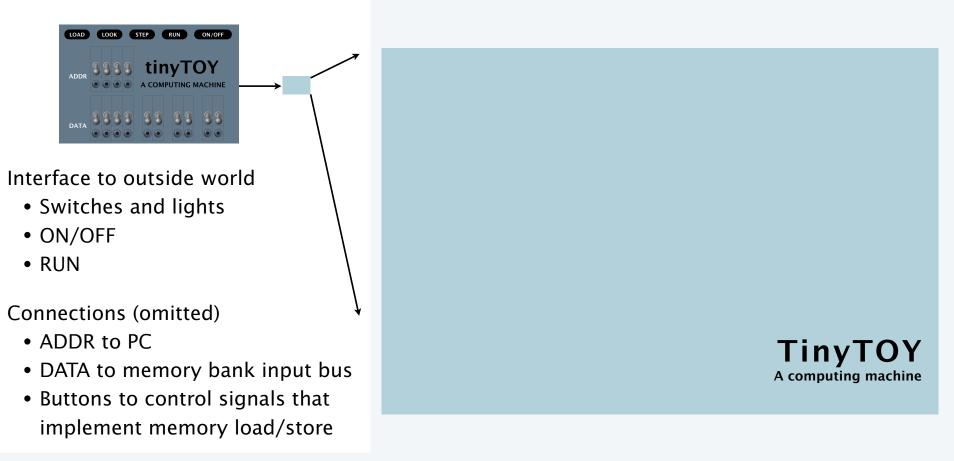

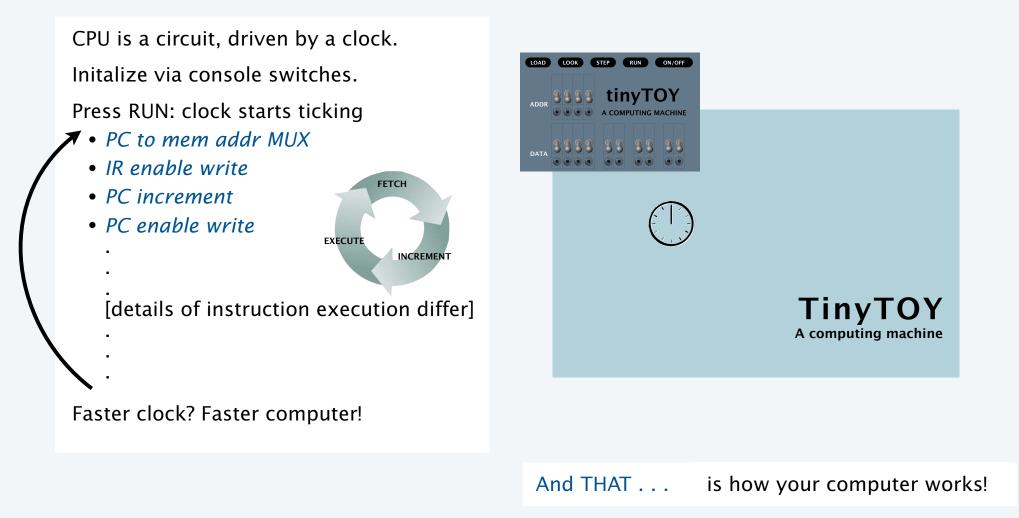

#### A smaller computing machine: TinyTOY

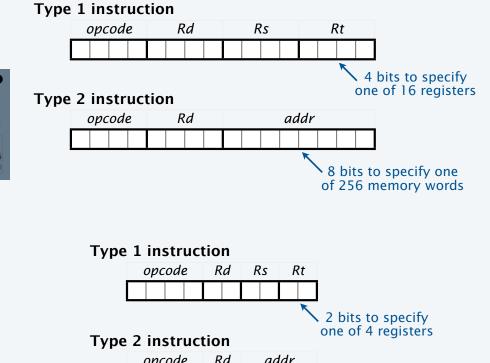

#### TOY instruction-set architecture.

- 256 16-bit words of memory.

- 16 16-bit registers.

- 1 8-bit program counter.

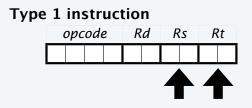

- 2 instruction types

- 16 instructions.

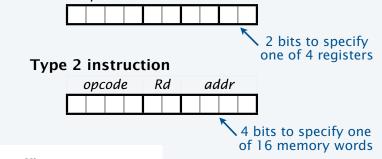

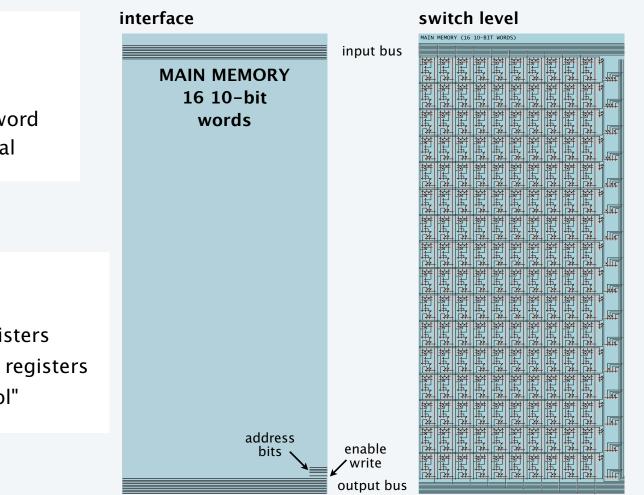

#### TinyTOY instruction-set architecture.

- 16 10-bit words of memory.

- 4 10-bit registers.

- 1 4-bit program counter.

- 2 instruction types

- 16 instructions.

Purpose of TinyTOY. Illustrate CPU circuit design for a "typical" computer.

#### Review: the state of the machine

Contents of memory, registers, and PC at a particular time

- Provide a record of what a program has done.

- Completely determines what the machine will do.

Memory

Registers

ALU

PC

Image: Sector S

ALU and IR hold intermedate states of computation

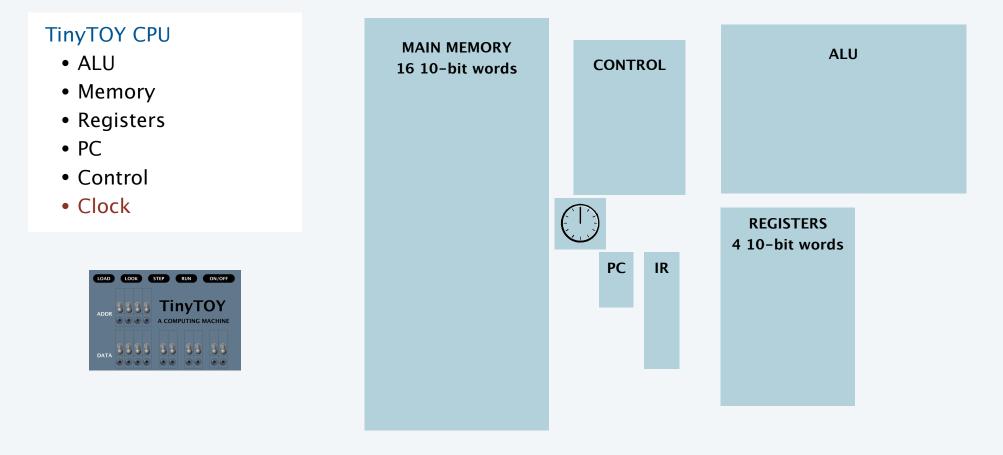

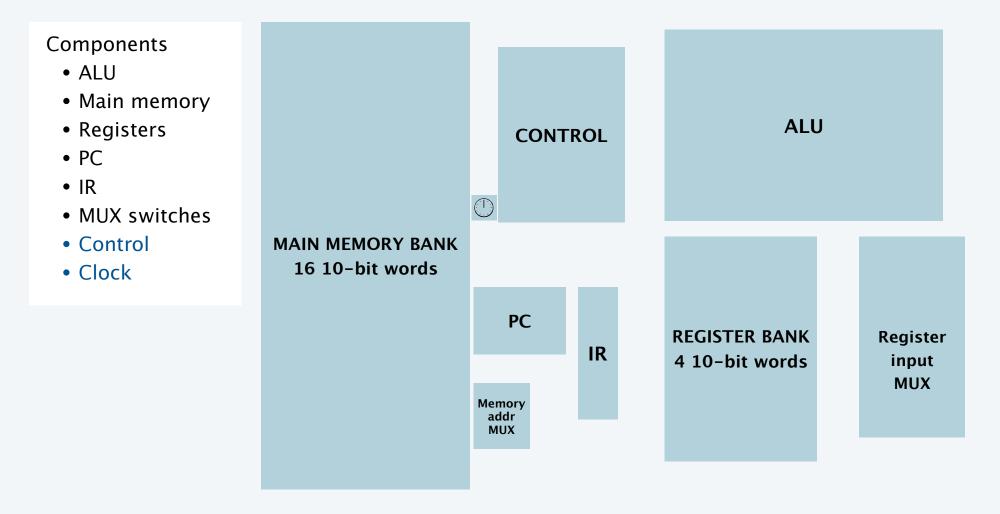

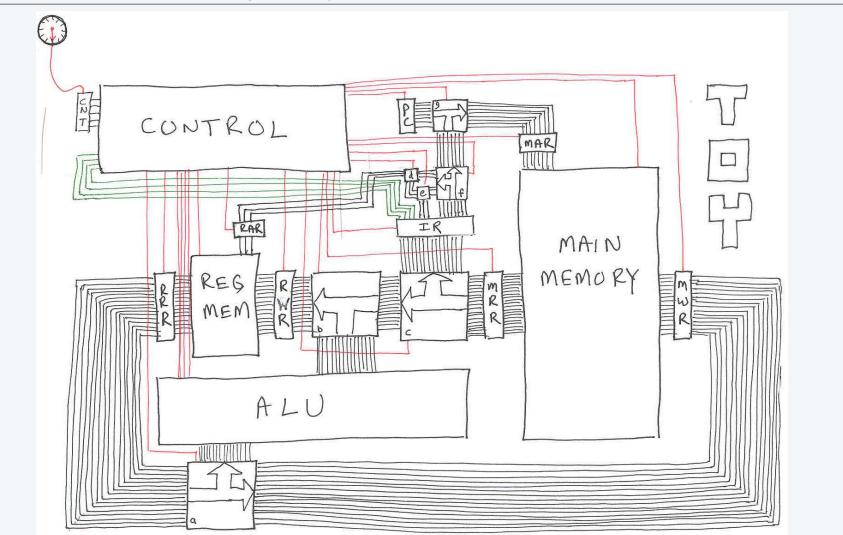

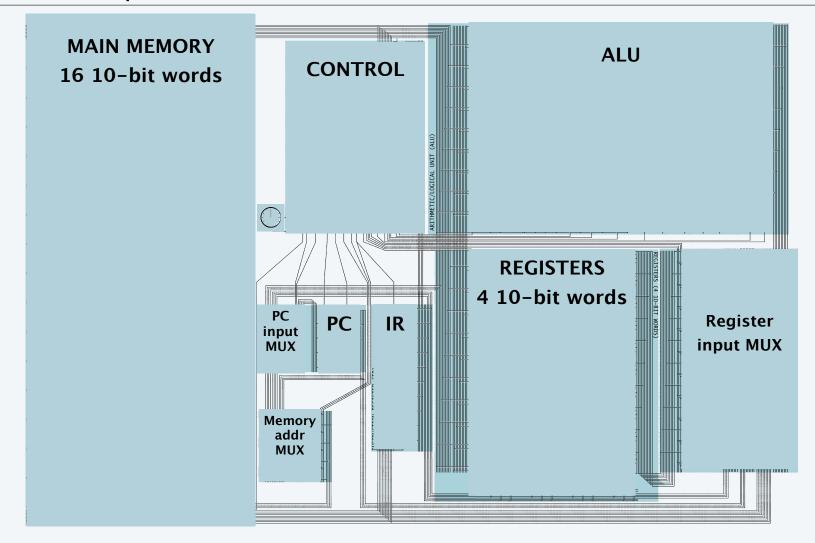

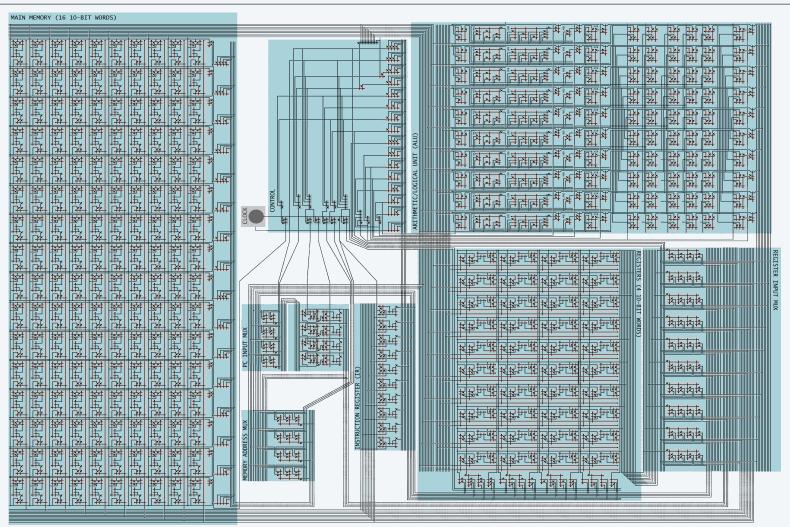

#### CPU circuit components for TinyTOY

Goal. Complete CPU circuit for TinyTOY (same design extends to TOY and to your computer).

#### Perspective

#### Q. Why TinyTOY?

A. Toy circuit width would be about 5 times TinyTOY circuit width.

Sobering fact. The circuit for your computer is *hundreds* to *thousands* of times wider.

Reassuring fact. Design of all three is based on the same fundamental ideas.

http://introcs.cs.princeton.edu

- Bits and registers

- Main memory and register banks

- Program counter

- Putting the pieces together

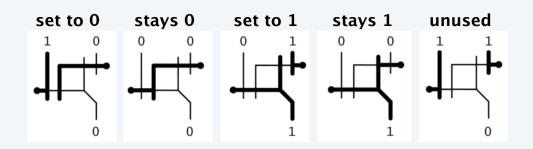

#### Sequential circuits

- Q. What is a sequential circuit?

- A. A digital circuit (all signals are 0 or 1) with feedback (loops).

- Q. Why sequential circuits?

- A. Memory (difference between a DFA and a Turing machine).

#### **Basic abstractions**

- On and off.

- Wire: Propagates an on/off value.

- Switch: Controls propagation of on/off values through wires.

- Flip-flop: *Remembers* a value.

#### A new ingredient: Circuits with memory

#### Feedback leads to circuits with one of two states

- Ex. two switches, each blocked by the other.

- State determined by whichever switches first.

- Stable (once set, state never changes).

#### An SR flip-flop is two cross-coupled NOR gates.

- Adds an extra line to each switch.

- R (reset) sets state to 0.

- S (set) sets state to 1.

Caveat. Timing of switch vs. propagation delay.

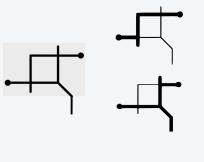

# classic notation components switches

Note. Feedback with three switches is *not* stable.

a "buzzer"

$$\rightarrow$$

$\checkmark$   $\checkmark$   $\checkmark$

10

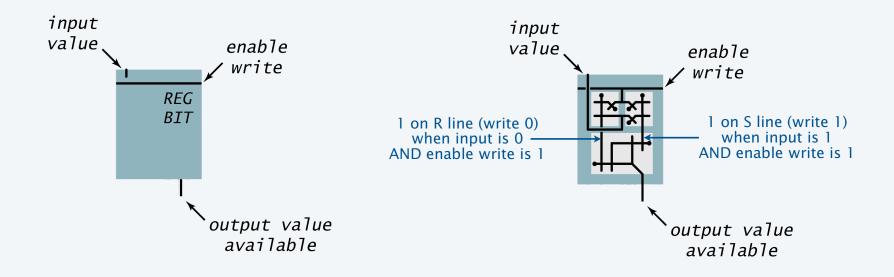

#### One bit in a processor register (PC and IR)

#### Add logic to an SR flip-flop for more precise control

- Provide data value on an input wire instead of using S and R controls.

- Use *enable write* signal to control timing of write.

- Flip-flop value is always available.

#### **Processor registers**

#### Processor registers (PC and IR)

- Store *W* bits.

- Input and output on *W*-wire busses.

- Register contents always available on output bus.

- When enable write is asserted, *W* input bits get copied into register.

- Ex 1. PC holds 4-bit address.

- Ex 2. IR holds 10-bit current instruction.

http://introcs.cs.princeton.edu

- Bits and registers

- Main memory and register banks

- Program counter

- Putting the pieces together

http://introcs.cs.princeton.edu

- Bits and registers

- Main memory and register banks

- Program counter

- Putting the pieces together

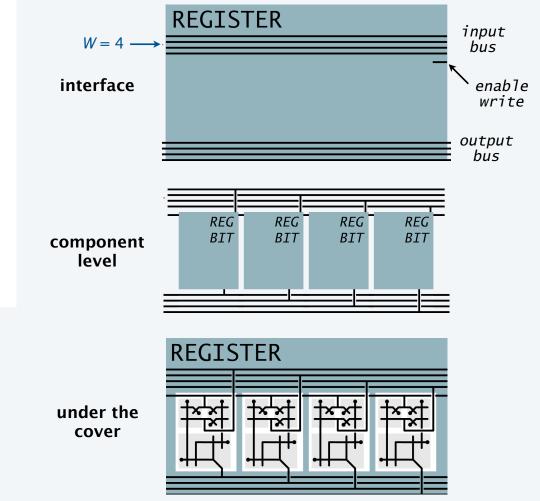

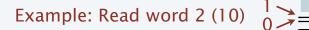

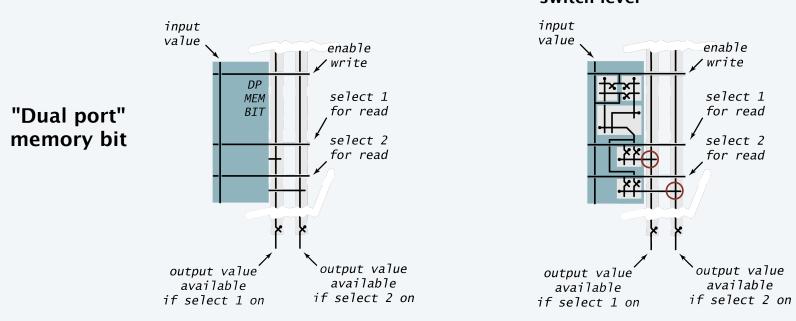

#### One bit in a main memory bank

#### Add a selection mechanism

- Flip-flop value is *not* always available.

- Use *select for read* signal to make it available.

- "1-hot" OR to collect the one bit value that is selected.

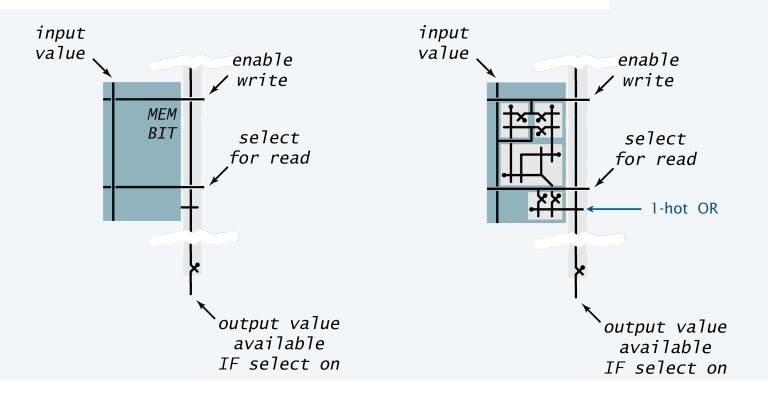

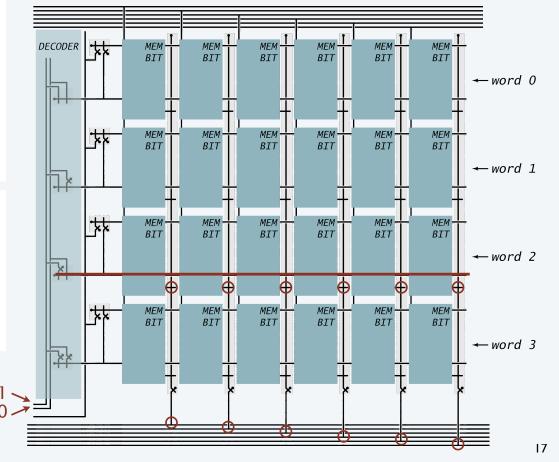

#### Main memory bank: interface

#### Main memory bank.

- Bank of *N* words; each stores *W* bits.

- Read and write data to one of *N* words.

- Address inputs select one word.

- Addressed word always on output bus.

- When write enabled, *W* input bits are copied into addressed word.

|               | number of<br>words | bits per<br>word | address<br>bits |

|---------------|--------------------|------------------|-----------------|

| this slide    | 4                  | 6                | 2               |

| tinyTOY       | 16                 | 10               | 4               |

| ΤΟΥ           | 256                | 16               | 8               |

| your computer | 1 billion          | 64               | 32              |

address 🔪

enable write \_\_\_\_

# interface MEMORY (four 6-bit words) -input bus ← output bus 16

#### Main memory bank: component level

#### Main memory bank.

- Bank of *N* words; each stores *W* bits.

- Read and write data to one of *N* words.

- Address inputs select one word.

- Addressed word always on output bus.

- When write enabled, *W* input bits are copied into addressed word.

#### Basic mechanisms

- A decoder uses address to switch on one line (through the addressed word)

- "1-hot" OR gates at each bit position take word contents to the output bus.

#### component-level implementation (four six-bit words)

#### Main memory bank: switch level

#### Main memory bank.

- Bank of *N* words; each stores *W* bits.

- Read and write data to one of *N* words.

- Address inputs select one word.

- Addressed word always on output bus.

- When write enabled, *W* input bits are copied into addressed word.

#### switch-level implementation

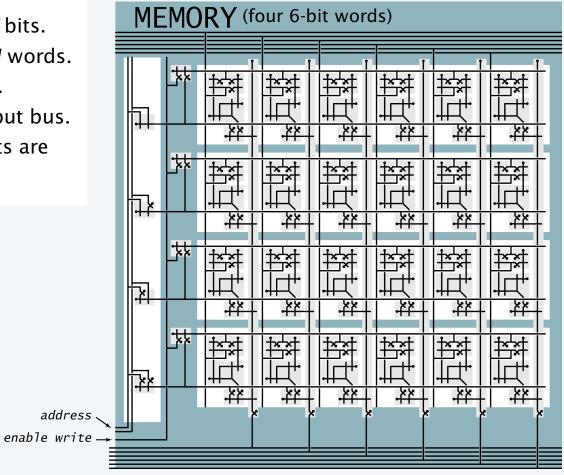

#### TinyTOY main memory bank

#### Interface

- Input bus for "store"

- Output bus for "load"

- Address bits to select a word

- Enable write control signal

#### Connections

- Input bus from registers

- Output bus to IR and registers

- Address bits from PC, IR, registers

- Enable write from "control"

#### One bit in a TinyTOY register bank

#### Need a second selection mechanism to read two registers at once

• Flip-flop value is *not* always available.

interface

- Use *select 1 for read* signal to make it available on output line 1.

- Use *select 2 for read* signal to make it available on output line 2.

- "1-hot" OR to collect the selected bit values on each line.

#### switch level

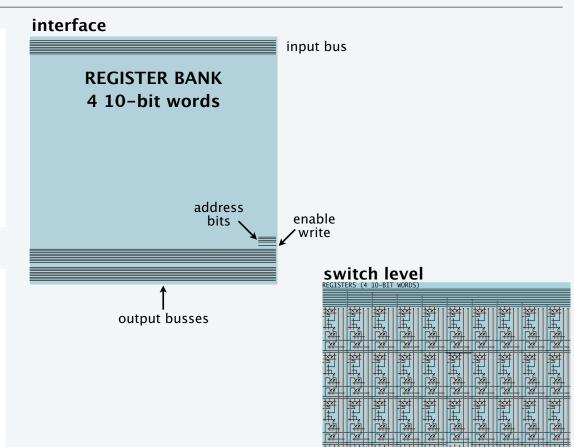

#### TinyTOY register bank

#### Interface

- Input bus

- Two output busses

- Address bits to select word

- Address bits to select 2nd word

- Enable write control signal

#### Connections

- Input bus from MUX (stay tuned)

- Output busses to ALU, memory

- Address bits from IR

- Enable write from "control"

http://introcs.cs.princeton.edu

- Bits and registers

- Main memory and register banks

- Program counter

- Putting the pieces together

http://introcs.cs.princeton.edu

- Bits and registers

- Main memory and register banks

- Program counter

- Putting the pieces together

#### Designing a digital circuit: overview

#### Steps to design a digital (sequential) circuit

- Design interface: input busses, output busses, control signals.

- Determine components.

- Determine datapath requirements: "flow" of bits.

- Establish control sequence.

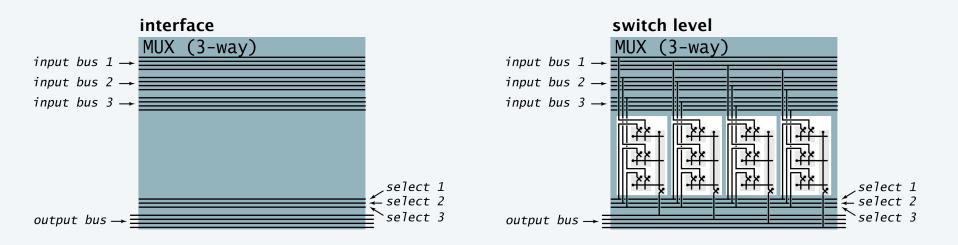

#### Another useful combinational circuit: Multiplexer

Multiplexer (MUX). Combinational circuit that selects among input buses.

- Puts bit values from input bus *i* onto output bus.

Typical use. Connect a component in different ways at different times.

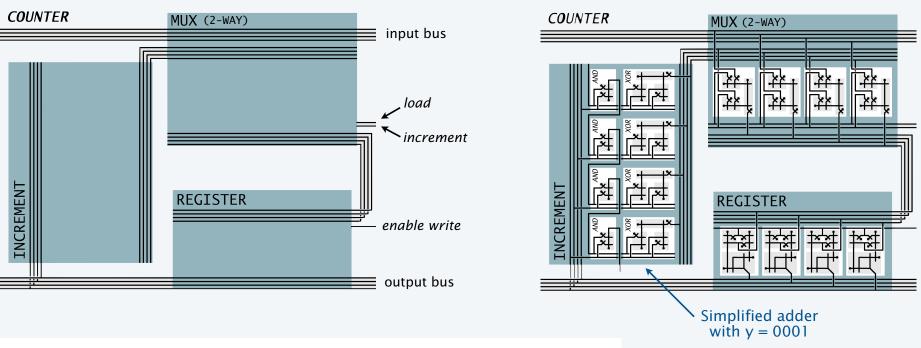

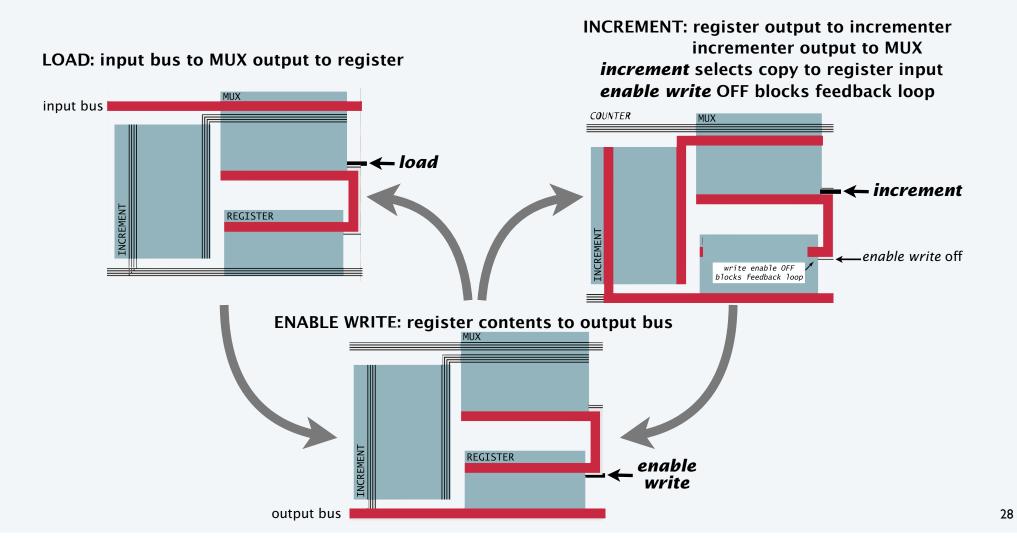

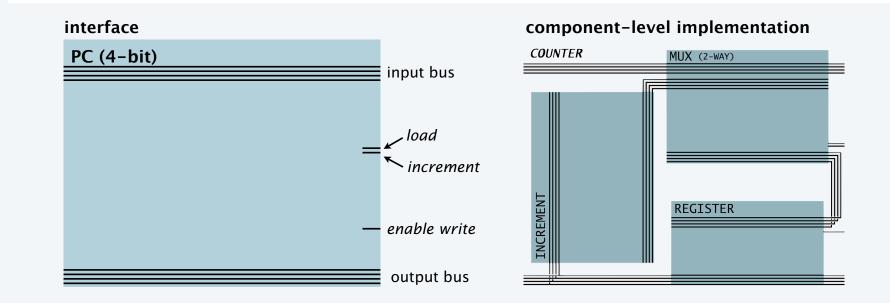

#### Counter interface

A *counter* holds a value that represents a binary integer and supports three control signals:

- *Load*. Set value from input bus.

- Increment. Add one to value.

- Enable write. Make value available on output bus.

Counter layout and implementation

component-level implementation

Layout and connections establish data paths where information travels.

#### switch-level implementation

Next: Sequence of control signals that effects desired behavior

#### Summary of TinyTOY PC circuit

The *program counter* holds an address and supports two control signal sequences:

- Load, then enable write. Set value from input bus (example: branch instruction).

- Increment, then enable write. Add one to value.

Value is written to an internal processor register and available on output bus in both cases.

Next. CPU circuit (10 components, 27 control signals).

http://introcs.cs.princeton.edu

- Bits and registers

- Main memory and register banks

- Program counter

- Putting the pieces together

http://introcs.cs.princeton.edu

- Bits and registers

- Main memory and register banks

- Program counter

- Putting the pieces together

#### TinyTOY: Interface

#### CPU is a circuit inside the machine

#### TinyTOY CPU components and layout

33

#### Review: Program counter and instruction register

TOY operates by executing a sequence of instructions.

#### Critical abstractions in making this happen

- Program Counter (PC). Memory address of next instruction.

- Instruction Register (IR). Instruction being executed.

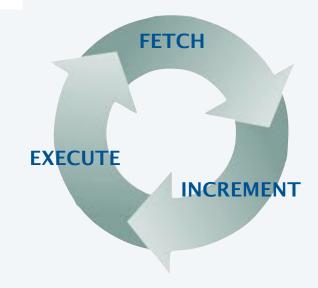

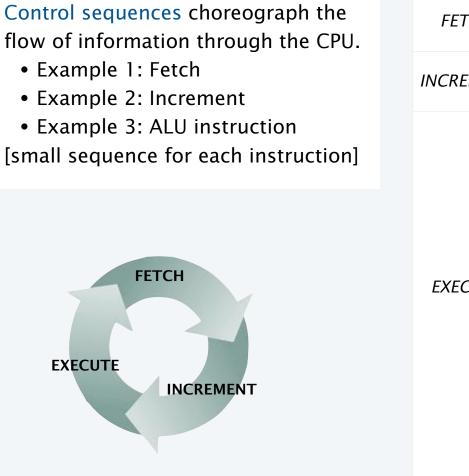

#### Fetch-increment-execute cycle

- Fetch: Get instruction from memory into IR.

- Increment: Update PC to point to *next* instruction.

- Execute: Move data to or from memory, change PC, or perform calculations, as specified by IR.

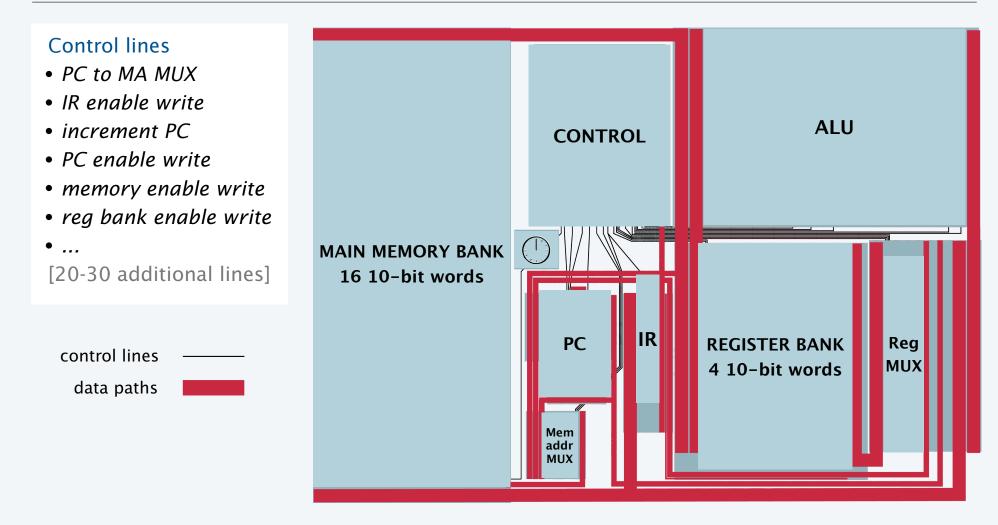

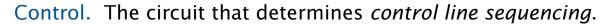

#### TinyTOY control lines and data paths

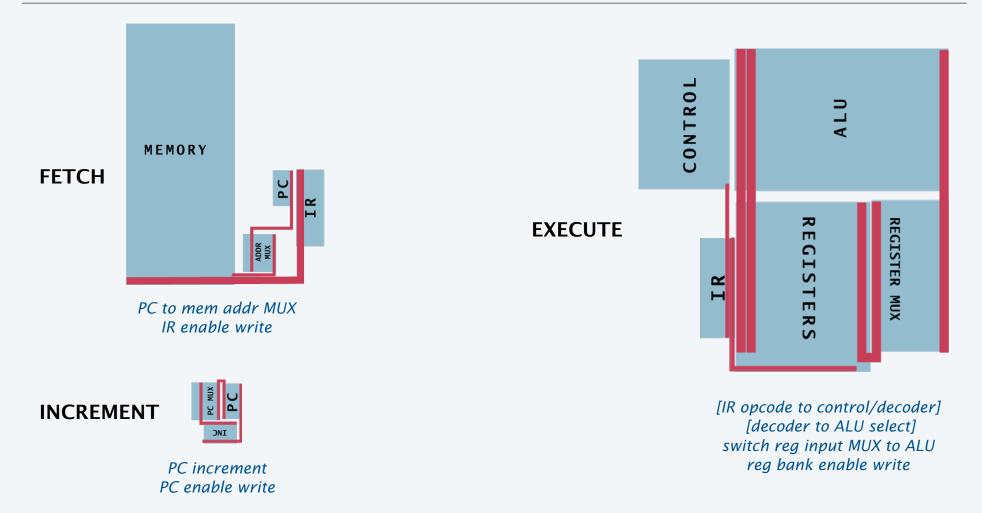

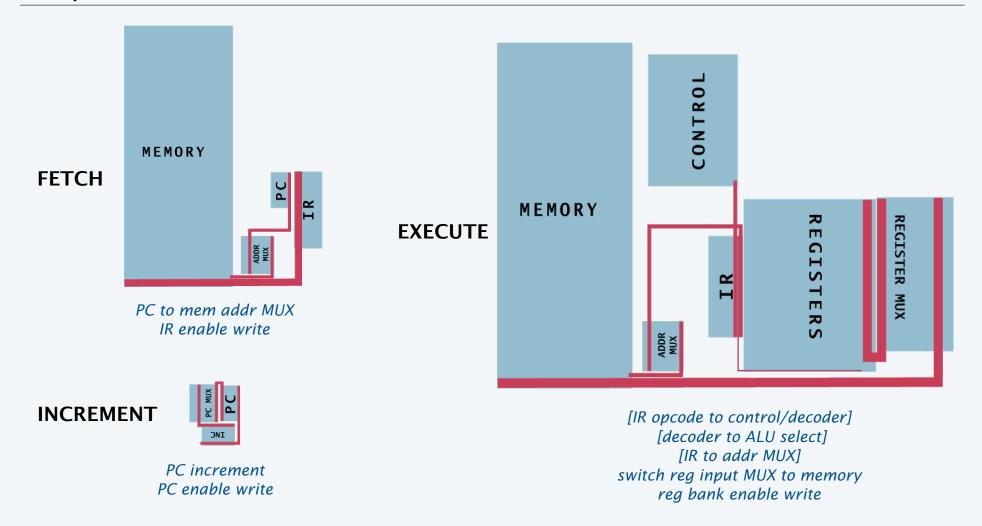

#### TinyTOY control sequences

| FETCH                                                              |   |                                 | PC to mem addr MUX<br>IR enable write             |  |

|--------------------------------------------------------------------|---|---------------------------------|---------------------------------------------------|--|

| INCREMENT                                                          |   |                                 | PC increment<br>PC enable write                   |  |

| 0<br>1<br>2<br>3<br>4<br>5<br>6<br><i>EXECUTE</i> 7<br>8<br>9<br>A | 0 | halt                            |                                                   |  |

|                                                                    | 1 | add                             | [IR opcode to decoder]<br>[decoder to ALU select] |  |

|                                                                    | 2 | subtract                        |                                                   |  |

|                                                                    | 3 | and                             |                                                   |  |

|                                                                    | 4 | xor switch reg input MUX to ALL |                                                   |  |

|                                                                    | 5 | shift left                      |                                                   |  |

|                                                                    | 6 | shift right                     |                                                   |  |

|                                                                    | 7 | load address                    |                                                   |  |

|                                                                    | 8 | load                            |                                                   |  |

|                                                                    | 9 | store                           |                                                   |  |

|                                                                    | А | load indirect                   |                                                   |  |

|                                                                    | В | store indirect                  |                                                   |  |

|                                                                    | С | branch zero                     |                                                   |  |

| C                                                                  |   | branch positive                 |                                                   |  |

|                                                                    | Е | jump register                   |                                                   |  |

|                                                                    | F | jump and link                   |                                                   |  |

#### Datapath for an add instruction

#### Datapath for a load instruction

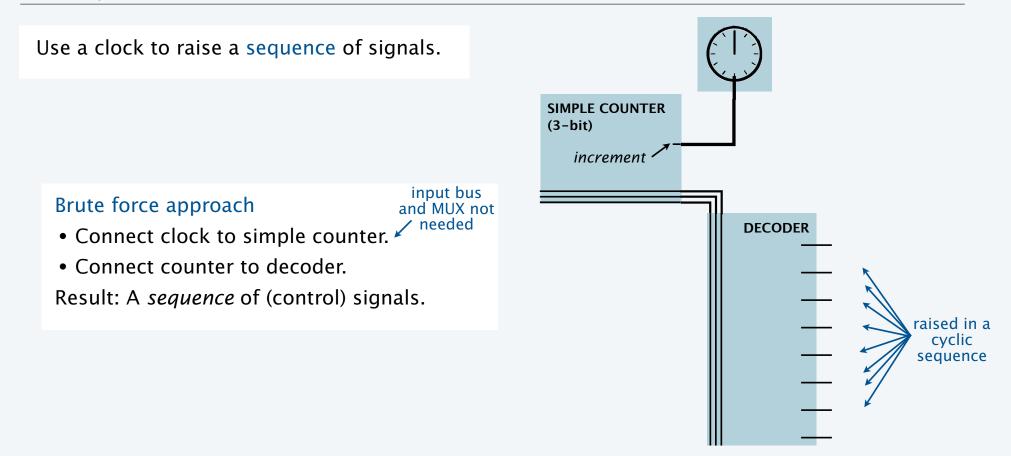

## Clock

A CLOCK provides a regular ON-OFF pulse.

Requirement. Clock cycle longer than max switching time.

Q. How to implement a clock?

- A. Use an external device.

- A. Use a buzzer.

TinyTOY A computing machine

#### Last step

Note. TinyTOY circuit (and your computer) uses a more efficient clocking scheme.

One final combinational circuit: Control

41

#### Tick-Tock

TOY "Classic", back-of-envelope design (circa 2005)

TinyTOY CPU component-level view

#### TinyTOY CPU switch-level view

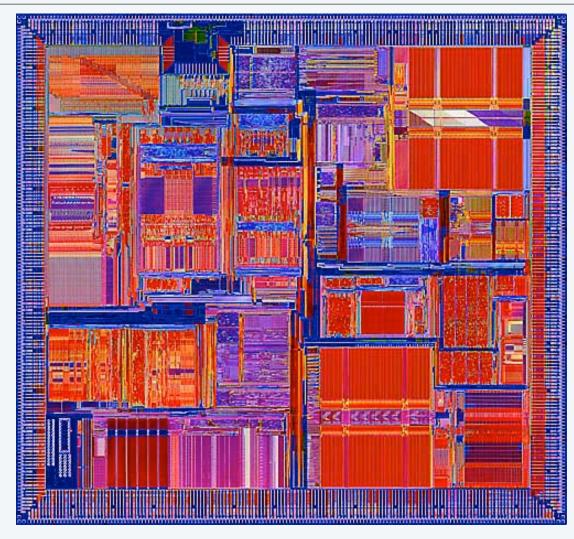

## A real microprocessor (MIPS R10000)

46

#### **COMPUTER SCIENCE** S E D G E W I C K / W A Y N E

http://introcs.cs.princeton.edu

- Bits and registers

- Main memory and register banks

- Program counter

- Putting the pieces together

**COMPUTER SCIENCE** S E D G E W I C K / W A Y N E

# Programming in Java

Robert Sedgewick • Kevin Wayne

An Interdisciplinary Approach

Sections 6.2 and 6.3

http://introcs.cs.princeton.edu

# **21. Central Processing Unit**