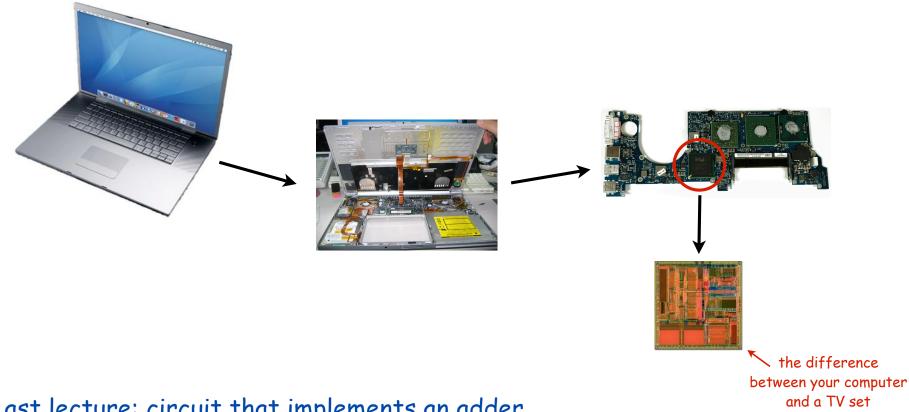

Let's build a computer!

CPU: "central processing unit"

computer: CPU + display + optical disk + metal case + power supply + ...

Last lecture: circuit that implements an adder

This lecture: circuit that implements a CPU

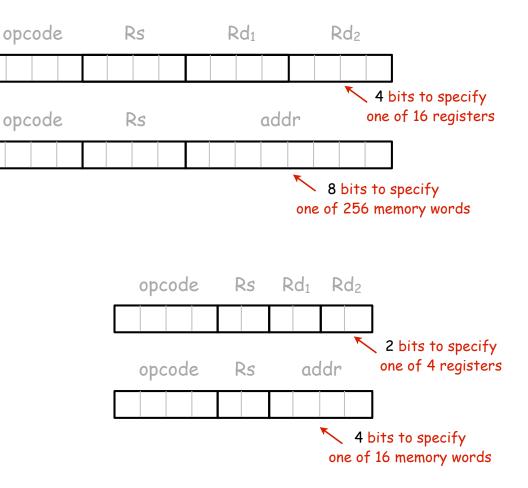

# TOY Lite

### TOY machine.

- 256 16-bit words of memory.

- 16 16-bit registers.

- 1 8-bit program counter.

- 2 instruction types

- 16 instructions.

### TOY-Lite machine.

- 16 10-bit words of memory.

- 4 10-bit registers.

- 1 4-bit program counter.

- 2 instruction types

- 16 instructions.

Goal: CPU circuit for TOY-Lite (same design extends to TOY, your computer)

Primary Components of Toy-Lite CPU

✓ Arithmetic and Logic Unit (ALU)

Memory

Toy-Lite Registers

Processor Registers: Program Counter and Instruction Register

"Control"

A New Ingredient: Circuits With Memory

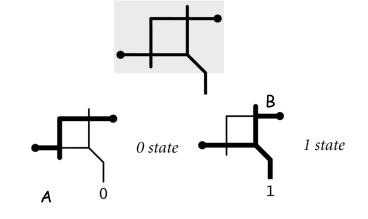

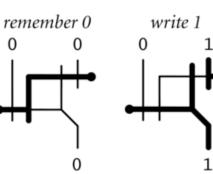

### Combinational circuits.

- Output determined solely by inputs.

- Ex: majority, adder, decoder, MUX, ALU.

### Sequential circuits.

- Output determined by inputs and current "state".

- Ex: memory, program counter, CPU.

- Ex. Simplest feedback loop.

- Two controlled switches A and B, both connected to power, each blocked by the other.

- State determined by whichever switches first.

- Stable.

Aside. Feedback with an odd number of switches is a buzzer (not stable). Doorbell: buzzer made with relays.

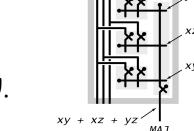

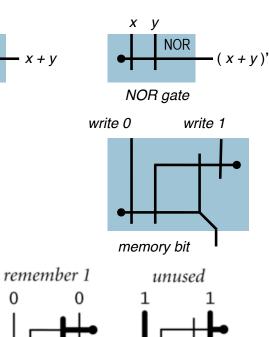

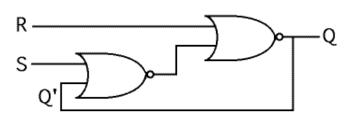

# SR Flip-Flop

### SR Flip-flop.

- Two cross-coupled NOR gates

- A way to control the feedback loop.

- Abstraction that "remembers" one bit.

- Basic building block for memory and registers.

x y

OR gate

OR

0

Caveats. Timing, switching delay.

0

# Memory Overview

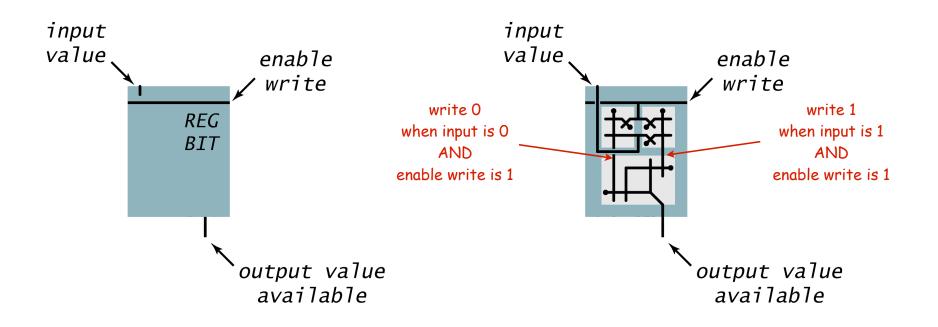

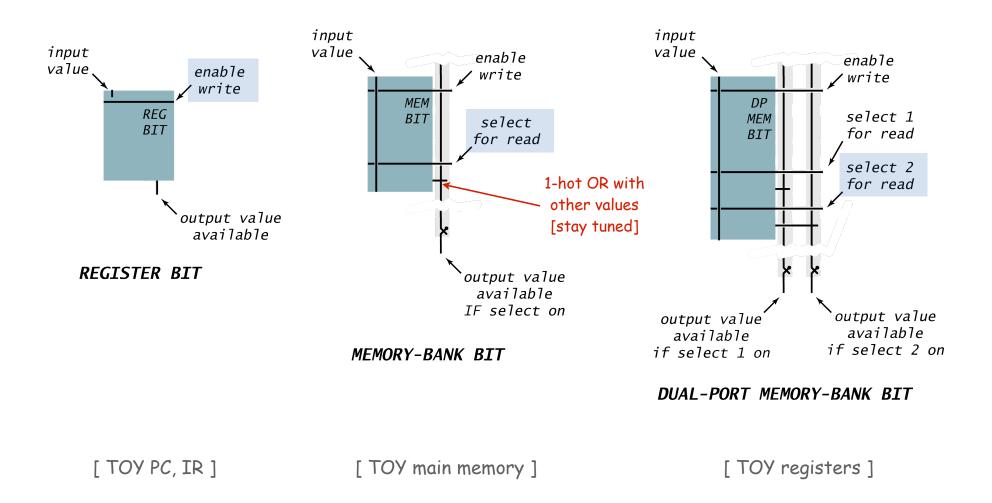

### Computers and TOY have several memory components.

- Program counter and other processor registers.

- TOY registers (4 10-bit words in Toy-Lite).

- Main memory (16 10-bit words in Toy-Lite).

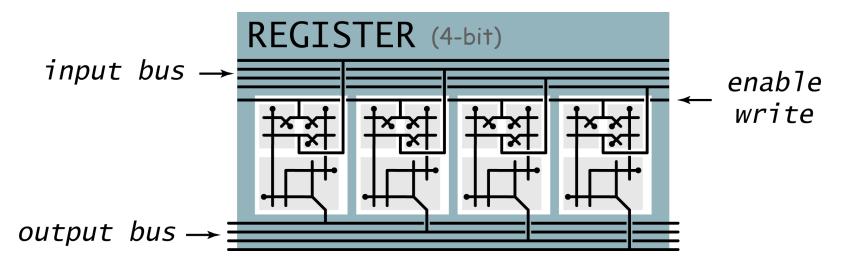

#### Implementation.

- Use one flip-flop for each bit of memory.

- Use buses and multiplexers to group bits into words.

#### Access mechanism: when are contents available?

- Processor registers: enable write.

- Main memory: select and enable write.

- TOY register: dual select and enable write

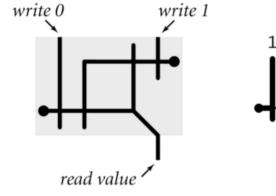

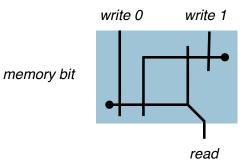

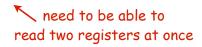

Processor register bit. Extend a flip-flop to allow easy access to values.

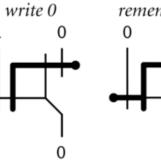

# Memory Bit Interface

#### Memory and TOY register bits: Add selection mechanism.

# Memory Bit: Switch Level Implementation

#### Memory and TOY register bits: Add selection mechanism.

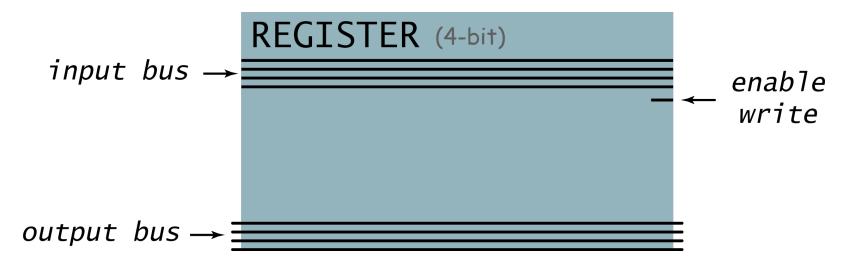

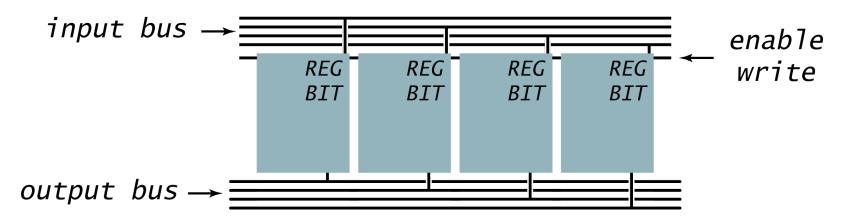

# Processor Register

**Processor register**.  $\leftarrow$  don't confuse with TOY register

- Stores k bits.

- Register contents always available on output bus.

- If enable write is asserted, k input bits get copied into register.

- Ex 1. TOY-Lite program counter (PC) holds 4-bit address.

- Ex 2. TOY-Lite instruction register (IR) holds 10-bit current instruction.

# Processor Register

**Processor register**. — don't confuse with TOY register

- Stores k bits.

- Register contents always available on output bus.

- If enable write is asserted, k input bits get copied into register.

- Ex 1. TOY program counter (PC) holds 8-bit address.

- Ex 2. TOY instruction register (IR) holds 16-bit current instruction.

# Processor Register

**Processor register**. — don't confuse with TOY register

- Stores k bits.

- Register contents always available on output bus.

- If enable write is asserted, k input bits get copied into register.

- Ex 1. TOY program counter (PC) holds 8-bit address.

- Ex 2. TOY instruction register (IR) holds 16-bit current instruction.

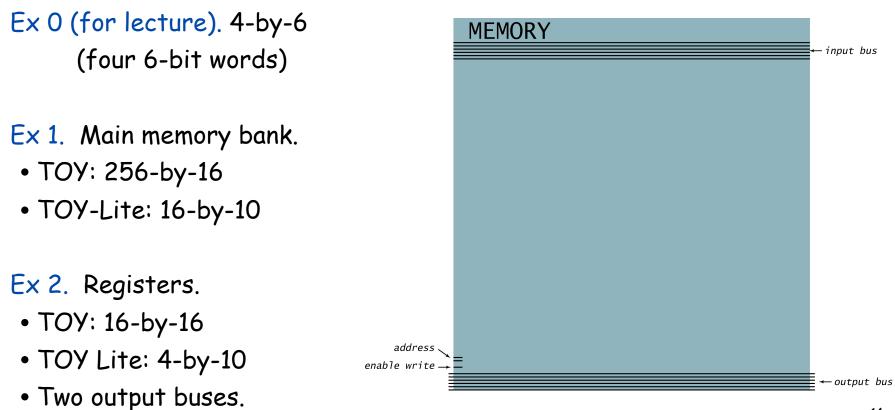

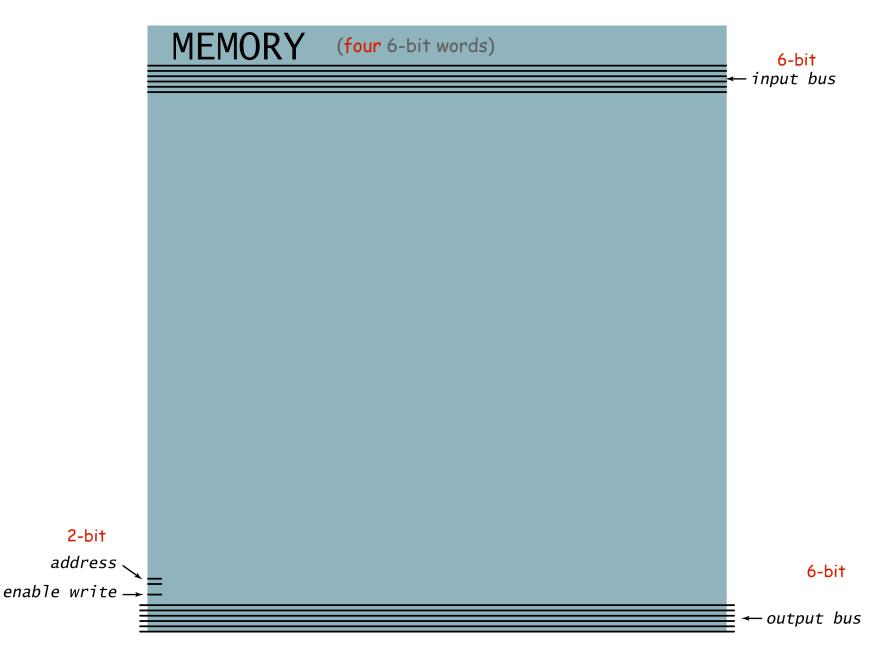

# Memory Bank

### Memory bank.

- Bank of n registers; each stores k bits.

- Read and write information to one of n registers.

- Address inputs specify which one. \_\_\_\_\_ log\_2n address bits needed

- Addressed bits always appear on output.

- If write enabled, k input bits are copied into addressed register.

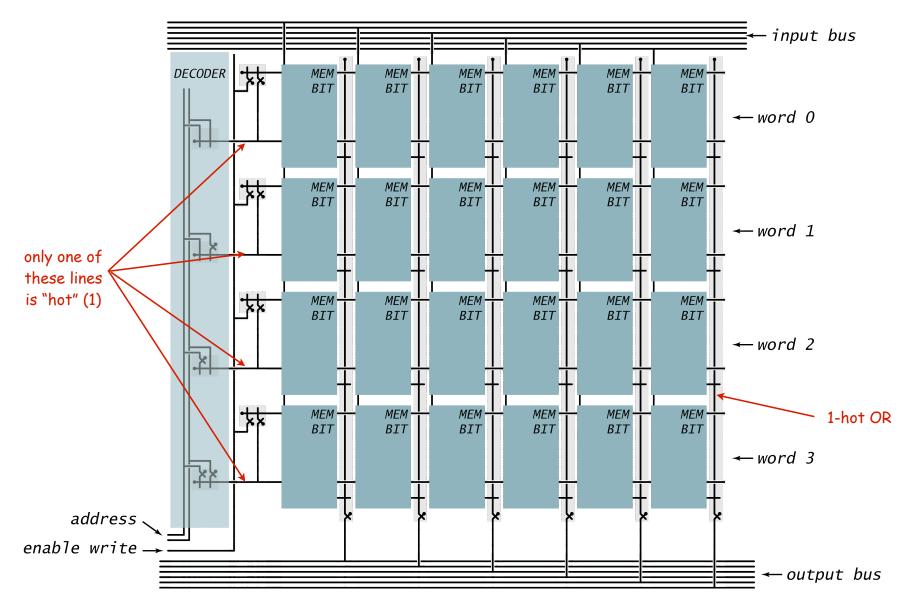

# Memory: Interface

### Memory: Component Level Implementation

#### Decoder plus memory selection: connect only to addressed word.

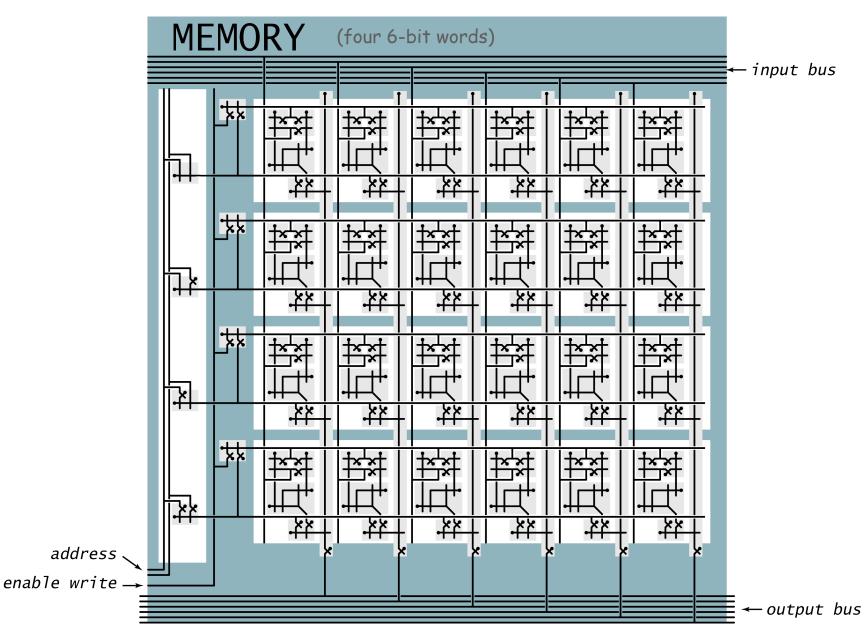

# Memory: Switch Level Implementation

# **TOY-Lite Memory**

### 16 10-bit words

- input connected to registers for "store"

- output connected to registers for "load"

- addr connect to processor Instruction Register (IR)

#### to registers (out)

|            | k   4  | 4        |          | j.  |                  | l lu     |     | Iy      | 14        | j.              | 14   | i iy | 14        |     |               |

|------------|--------|----------|----------|-----|------------------|----------|-----|---------|-----------|-----------------|------|------|-----------|-----|---------------|

| 4 <u>5</u> |        |          |          |     |                  |          |     |         |           |                 |      |      |           |     |               |

| IIII       | *****  | 燕나려      |          |     |                  | क्रम्द्र | 新城적 |         |           | <u>क्र</u> म्ये |      |      |           |     |               |

|            | 천 꼬나 찬 | 游관       | 游관       | 游관  | 游과천              | 游관       |     | 游내神     | 游규추       |                 | 滿고주천 | 游관   | 游규추       | 海과천 | <u>क्रम</u> क |

|            | 철학교철   | क्रम्द्र | क्रम्द्र | 堂년철 | 猫城               | क्रम्द्र | 教理な | 遊せな     | 猫哇        | あせな             | 游년   | 游년석  | 猫哇        | 猫哇  | 菊叶绿           |

| 「茶」は       | 천 빛내 천 | 猫哇       | 游내려      | 猫哇  | 猫哇萨              | 滿고(천     | 猫哇萨 | 猫哇萨     | 猫哇科       | 教社会             | 猫哇   | 菊堆茶  | 滿급        | 菊堆落 | あれな           |

|            | 철찾규수천  | 滿며현      | 游년천      | 滿고  | 滿급               | क्रीम्टे | 滿고  | 滿고      | 猫哇        | 滿나촌             | 滿고   | 滿고   | क्रीन्ट्र | 茶卉を |               |

| 對山         | 철학교관   | 滿고       | 游내さ      | 猫哇  | 猫哇               | क्रीमंटे | 猫哇  | 猫哇      | 猫哇        | 満せる             | 滿고   | 茶卉を  | 猫哇        | 猫哇萨 |               |

| 對山         | 참꼬규찬   | 滿고       | 游년천      | 滿고주 | 滿고               | 游년천      | 滿고  | 猫哇      | 描내려       | 游년천             | 滿고   | 茶卉な  | 滿급        | 猫哇  |               |

|            | 철학교철   | 教理な      | 游년천      | 猫哇  | 猫哇               | 游년천      | 菊堆落 | 菊草      | 満せる       | 菊枝              | 満せる  | 教理な  | 満せる       | 教理な |               |

| - <u>*</u> | 철학교관   | 游년천      | 游년천      | 游년천 | 游관               | 禁년천      | 禁년천 | 菊草      | क्रीम्द्र | 游년천             | 禁止   | 教理な  | क्रीम्ट्र | 教理な | 教理な           |

| मिक        | 철학교철   | 満せな      | 塑理等      | 教理な | क <u>्र</u> म्ये | क्रमंत्र | 教理な | क्रम्ये | क्रम्ये   | क्रम्ये         | 教理な  | 游내려  | क्रम्ये   | 游년천 | 教理な           |

to registers (in)

to IR •

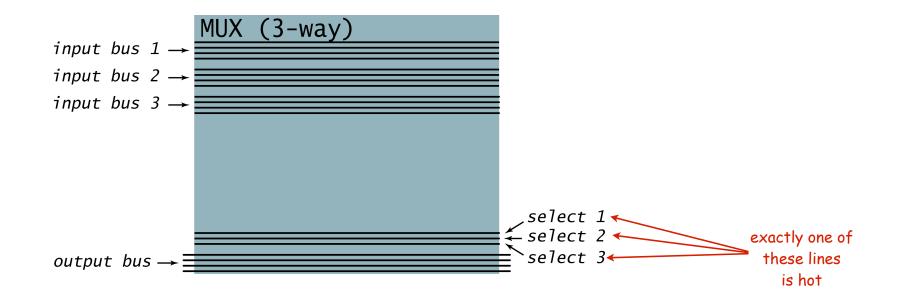

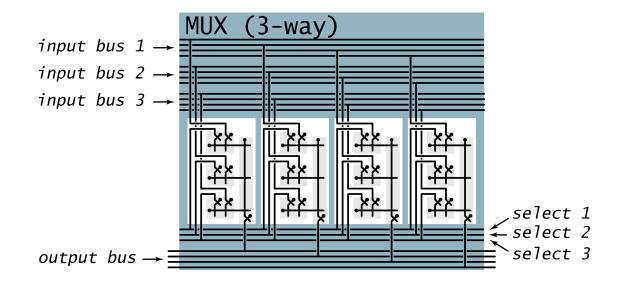

Another Useful Combinational Circuit: Multiplexer

Multiplexer (MUX). Combinational circuit that selects among input buses.

- Exactly one select line i is activated.

- Copies bits from input bus i to output bus.

### Nuts and Bolts: Buses and Multiplexers

Multiplexer (MUX). Combinational circuit that selects among input buses.

- Exactly one select line i is activated.

- Copies bits from input bus i to output bus.

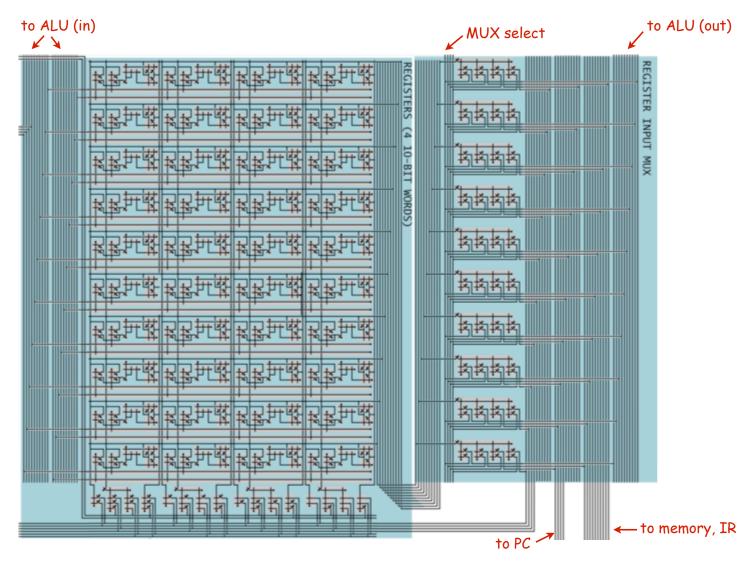

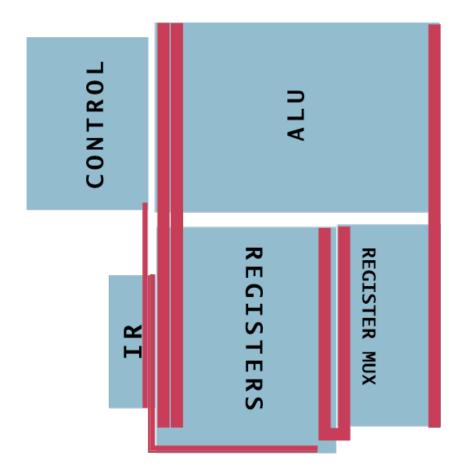

# Toy-Lite Registers

# 4 10-bit words

- Dual-ported to support connecting two different registers to ALU

- Input MUX to support input connection to ALU, memory, IR, PC

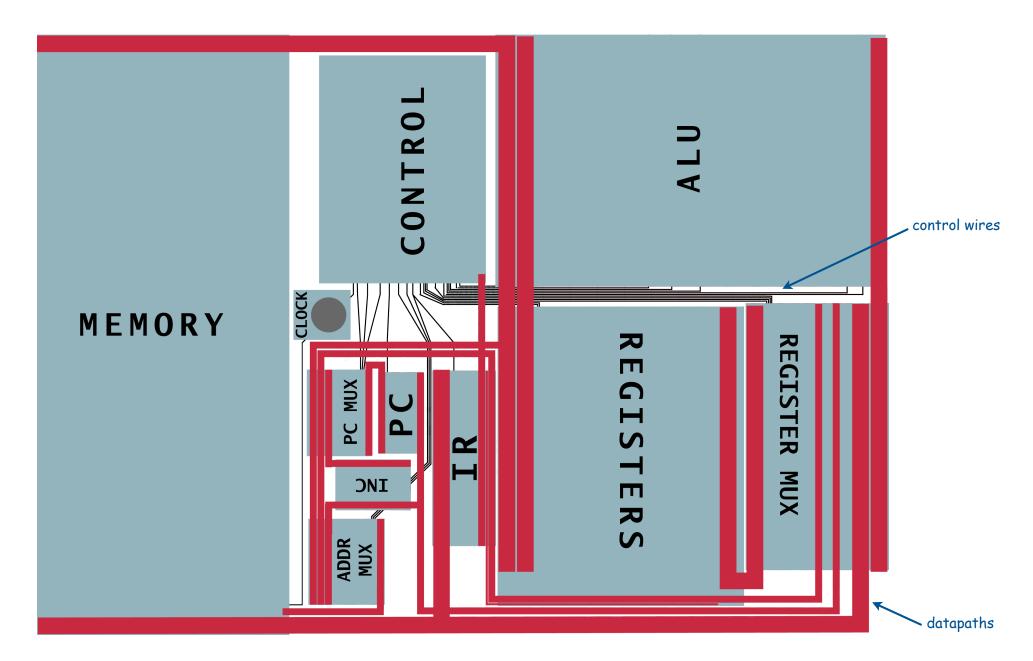

# Primary Components of Toy-Lite CPU

✓ ALU

Memory

✓ Registers

Processor Registers: Program Counter and Instruction Register

Not quite done. Need to be able to increment.

"Control"

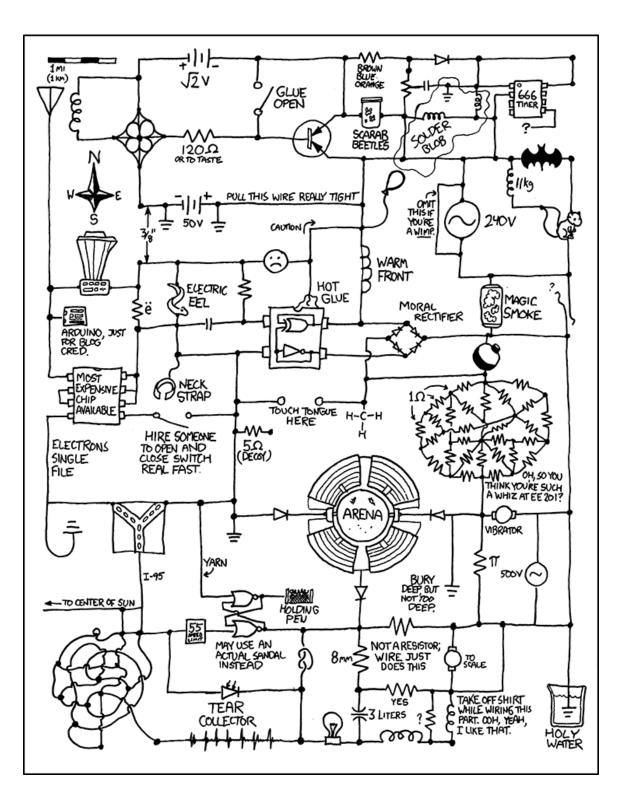

# How To Design a Digital Device

### How to design a digital device.

- Design interface: input buses, output buses, control wires.

- Determine components.

- Determine datapath requirements: "flow" of bits.

- Establish control sequence.

Warmup. Design a program counter (3 devices, 3 control wires).

Goal. Design TOY-Lite computer (10 devices, 27 control wires).

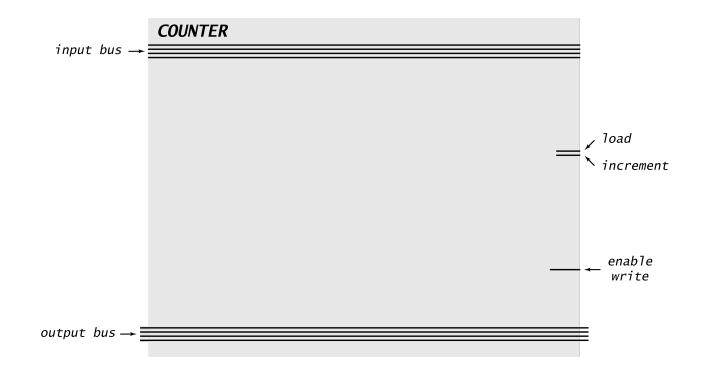

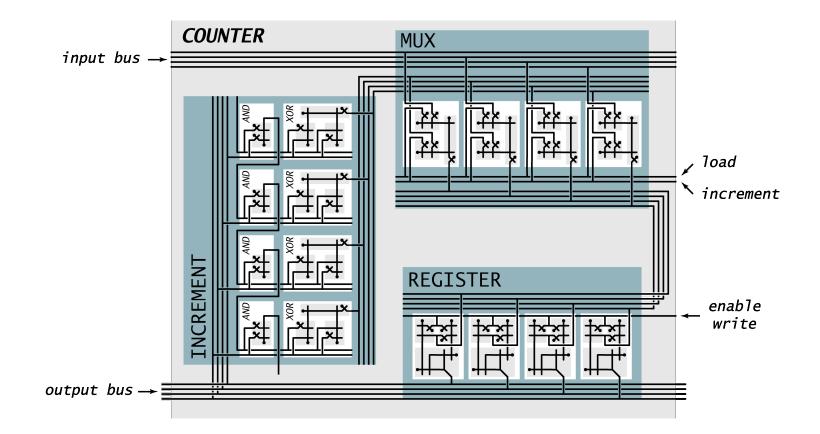

# Program Counter: Interface

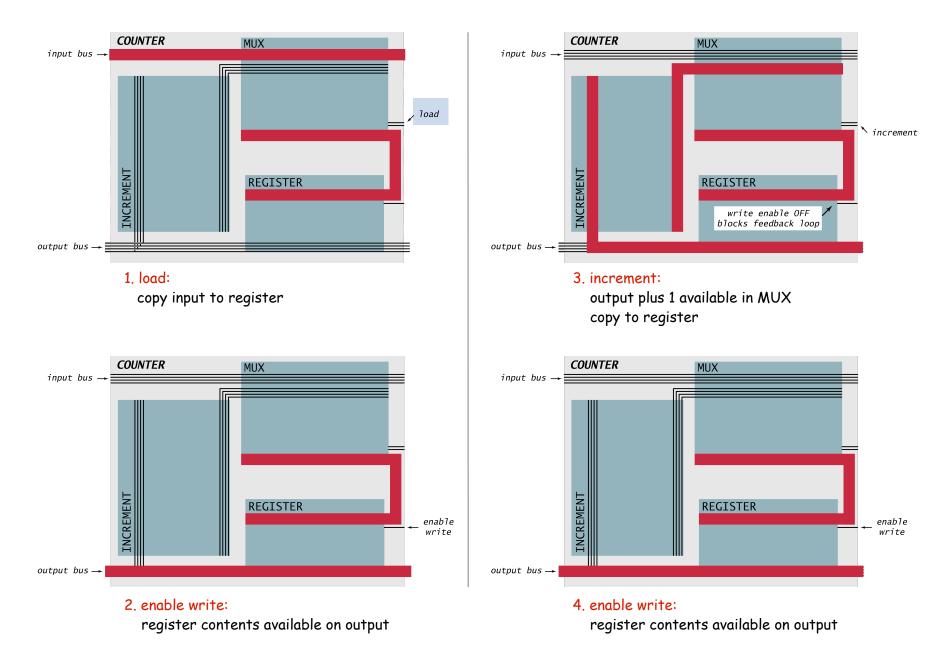

Counter. Holds value that represents a binary number.

- Load: set value from input bus.

- Increment: add one to value.

- Enable Write: make value available on output bus.

Ex. TOY-Lite program counter (4-bit).

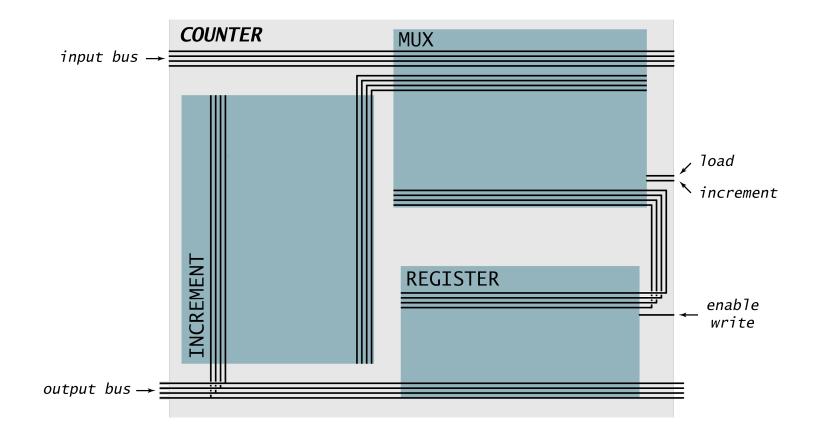

# Program Counter: Components

# Components.

- Register.

- Incrementer.

- Multiplexer (to provide connections for both load and increment).

Datapath.

- Layout and interconnection of components.

- Connect input and output buses.

Control. Choreographs the "flow" of information on the datapath.

Datapath.

- Layout and interconnection of components.

- Connect input and output buses.

Control. Choreographs the "flow" of information on the datapath.

Datapath.

- Layout and interconnection of components.

- Connect input and output buses.

Control. Choreographs the "flow" of information on the datapath.

# Primary Components of Toy-Lite CPU

🗸 ALU

✓ Memory

✓ Toy-Lite Registers

Processor Registers: Program Counter and Instruction Register

"Control"

# How To Design a Digital Device

### How to design a digital device.

- Design interface: input buses, output buses, control wires.

- Determine components.

- Determine datapath requirements: "flow" of bits.

- Establish control sequence.

Warmup. Design a program counter (3 devices, 3 control wires).

Next. Design TOY-Lite computer (10 devices, 27 control wires).

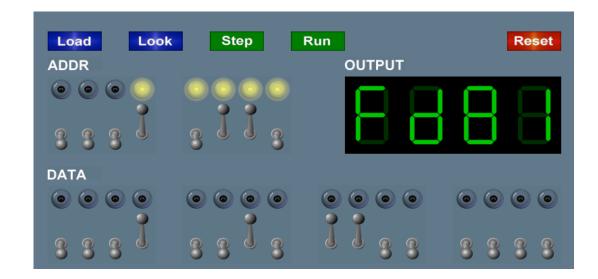

# TOY-Lite: Interface

#### CPU is a circuit.

### Interface: switches and lights.

- set memory contents

- set PC value

- press RUN

- [details of connection to circuit omitted]

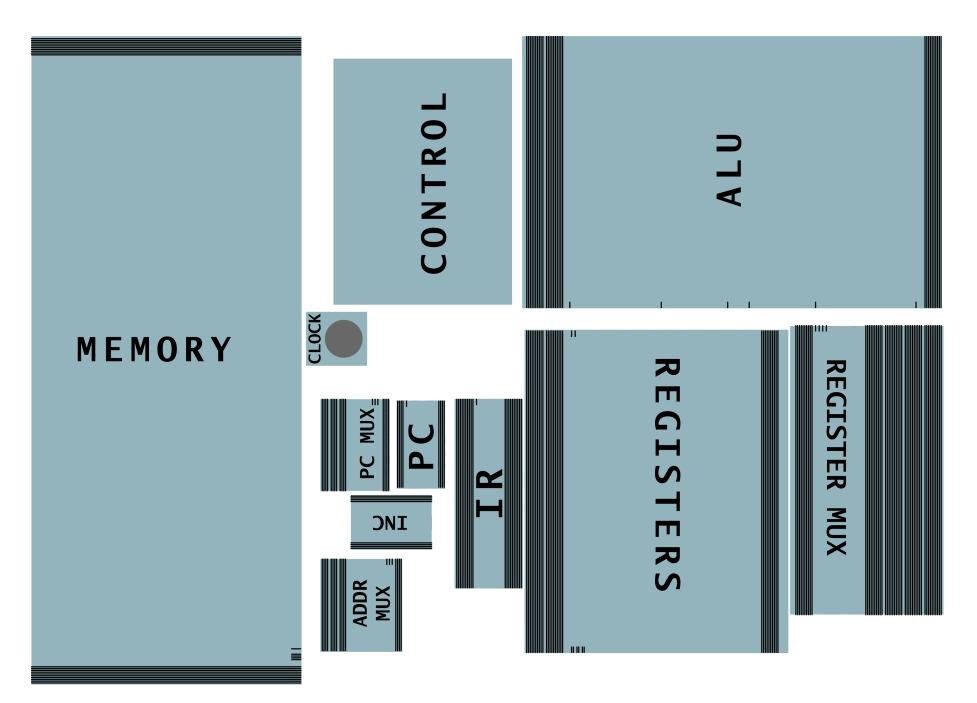

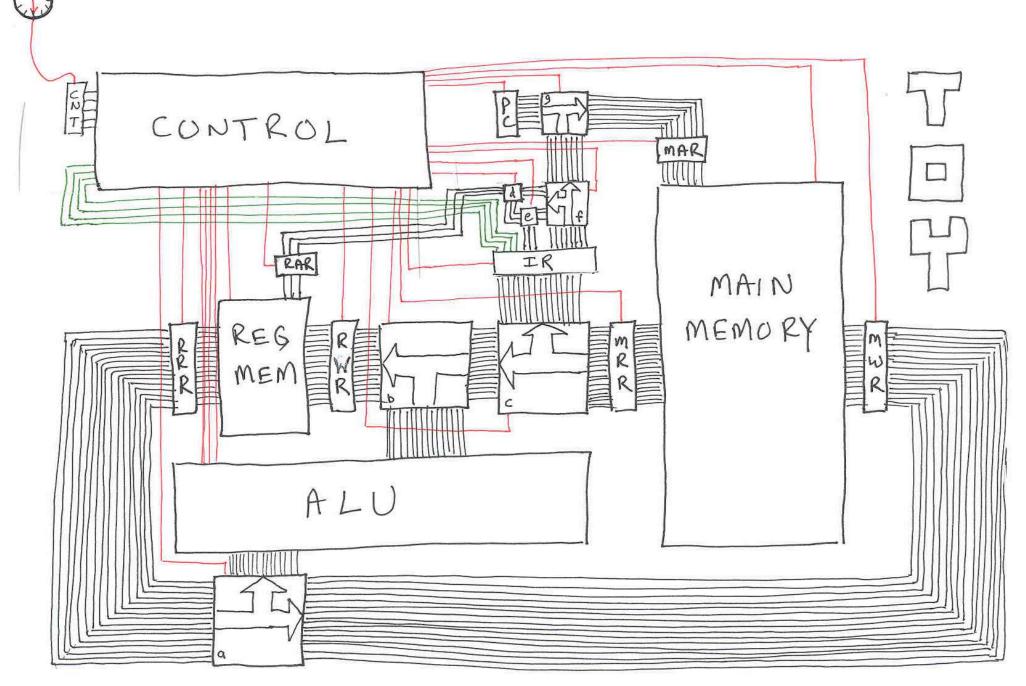

TOY-Lite: Components

TOY-Lite: Layout

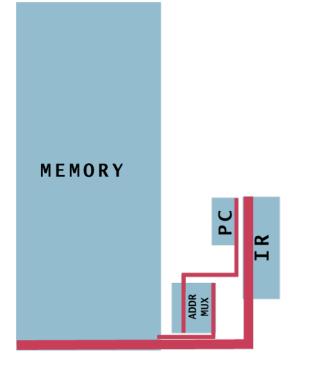

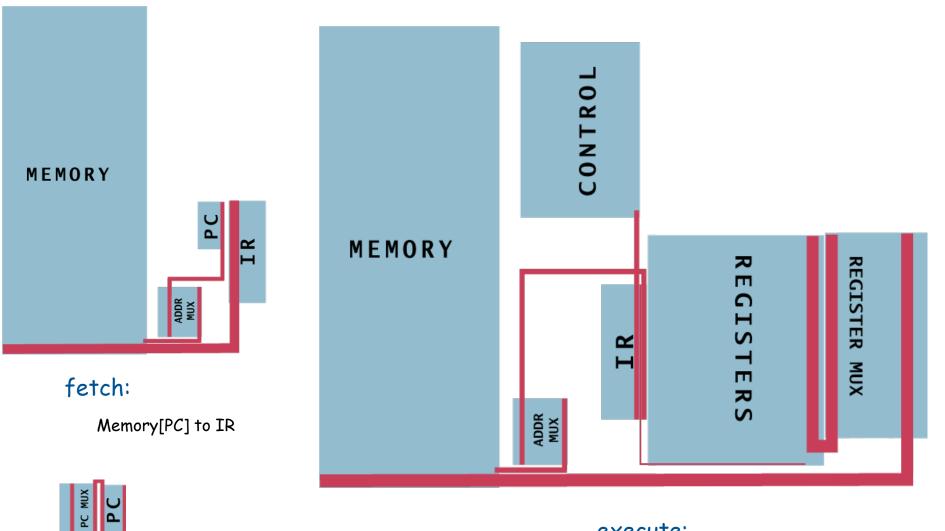

# TOY-Lite Datapath Requirements: Fetch

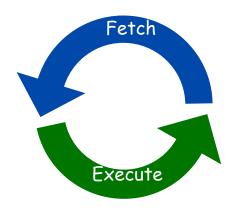

### Basic machine operation is a cycle.

- Fetch

- Execute

# Fetch.

- Memory[PC] to IR

- Increment PC

### Execute.

• Datapath depends on instruction

# TOY-Lite Datapath Requirements: Execute

#### Instructions determine datapaths and control sequences for execute

|   |                 | •••                  |

|---|-----------------|----------------------|

| 0 | halt            |                      |

| 1 | add             |                      |

| 2 | subtract        | IR opcode to control |

| 3 | and             | control to ALU       |

| 4 | xor             | two registers to ALU |

| 5 | shift left      | ALU to register MUX  |

| 6 | shift right     |                      |

| 7 | load address    |                      |

| 8 | load            |                      |

| 9 | store           |                      |

| A | load indirect   |                      |

| В | store indirect  |                      |

| С | branch zero     |                      |

| D | branch positive |                      |

| E | jump register   | •••                  |

| F | jump and link   |                      |

TOY-Lite: Datapaths and Control

Datapath: Add

fetch:

Memory[PC] to IR

increment PC

#### execute:

IR opcode to control control to ALU two registers to ALU ALU to register MUX

## Datapath: Load

#### execute:

IR opcode to control IR to addr MUX memory to register MUX

increment increment PC

ONI

#### Last step

Control. Each instruction corresponds to a sequence of control signals.

- Q. How do we create the sequence?

- A. Need a "physical" clock.

Solution 2: Use a buzzer [need sufficiently long cycle to cover CPU switching]

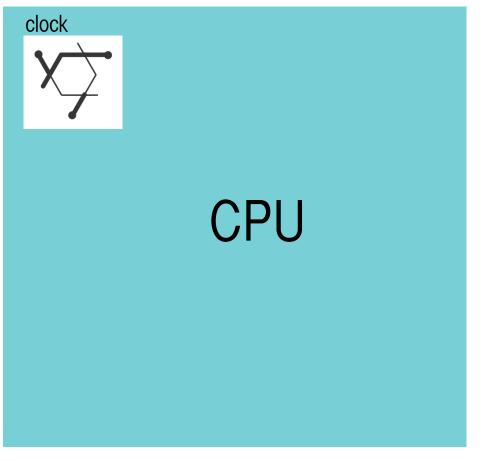

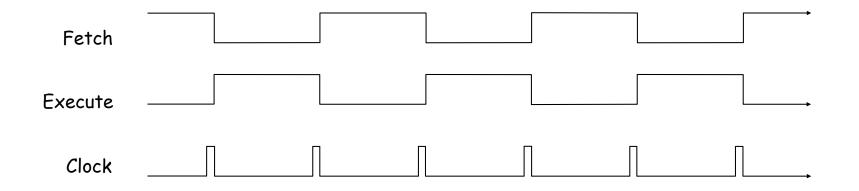

# Clock

# Clock.

- Fundamental abstraction: regular on-off pulse.

- -on: fetch phase

- -off: execute phase

- "external" device.

- Synchronizes operations of different circuit elements.

- Requirement: clock cycle longer than max switching time.

Execute

Solution 3?

#### Fetch

### How much does it Hert?

#### Frequency is inverse of cycle time.

- Expressed in hertz.

- <sup>•</sup> Frequency of 1 Hz means that there is 1 cycle per second.

- -1 kilohertz (kHz) means 1000 cycles/sec.

- -1 megahertz (MHz) means 1 million cycles/sec.

- -1 gigahertz (GHz) means 1 billion cycles/sec.

- -1 terahertz (THz) means 1 trillion cycles/sec.

Heinrich Rudolf Hertz (1857-1894)

# Clocking Methodology

#### Two-cycle design.

- Each control signal is in one of four epochs.

- -fetch

- fetch and clock

- execute

- execute and clock

[set memory address from pc]

[write instruction to IR]

[set ALU inputs from registers]

[write result of ALU to registers]

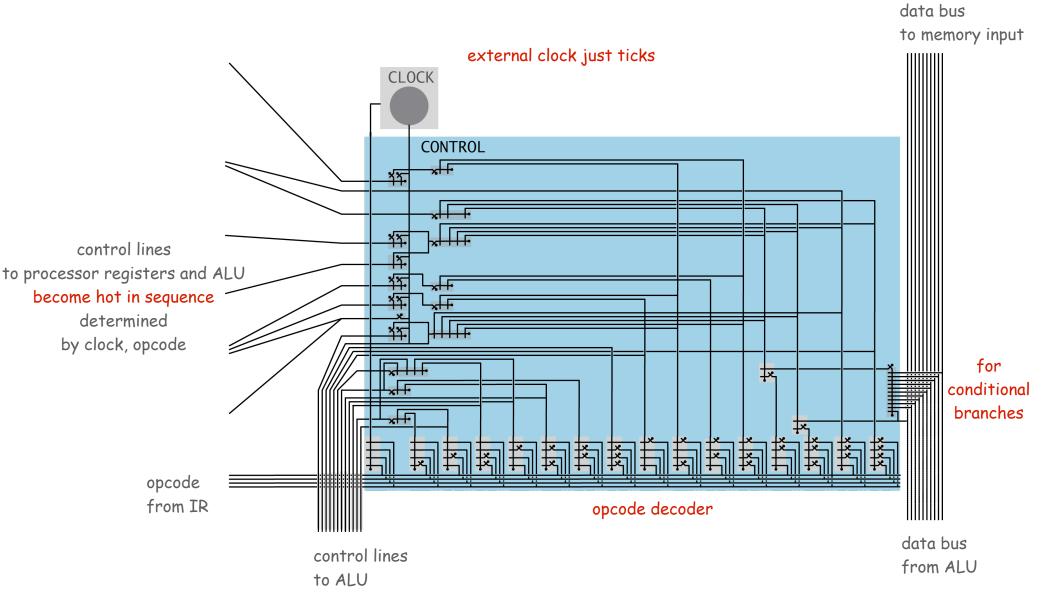

### One Last Combinational Circuit: Control

Control. Circuit that determines control line sequencing.

# Tick-Tock

CPU is a circuit, driven by a clock.

Switches initialize memory, PC contents

#### Clock ticks

- fetch instruction from memory[PC] to IR

- increment PC

- execute instruction

[details of instruction execution differ]

- fetch next instruction

- ...

That's all there is to it!

TOY "Classic", Back Of Envelope Design

### TOY-Lite CPU

MAIN MEMORY (16 10-BIT WORDS)

| MAIN MEMORY (10 10-BIT WORDS)                |              |  |

|----------------------------------------------|--------------|--|

|                                              |              |  |

|                                              |              |  |

|                                              |              |  |

|                                              |              |  |

|                                              |              |  |

|                                              |              |  |

|                                              |              |  |

|                                              |              |  |

|                                              |              |  |

|                                              |              |  |

|                                              |              |  |

|                                              |              |  |

|                                              |              |  |

|                                              | PC INPUT MUX |  |

|                                              |              |  |

|                                              |              |  |

|                                              |              |  |

| <u>الج الج الج الح الح الح الح الح الح ا</u> |              |  |

|                                              |              |  |

|                                              |              |  |

|                                              |              |  |

REGISTER INPUT MUX

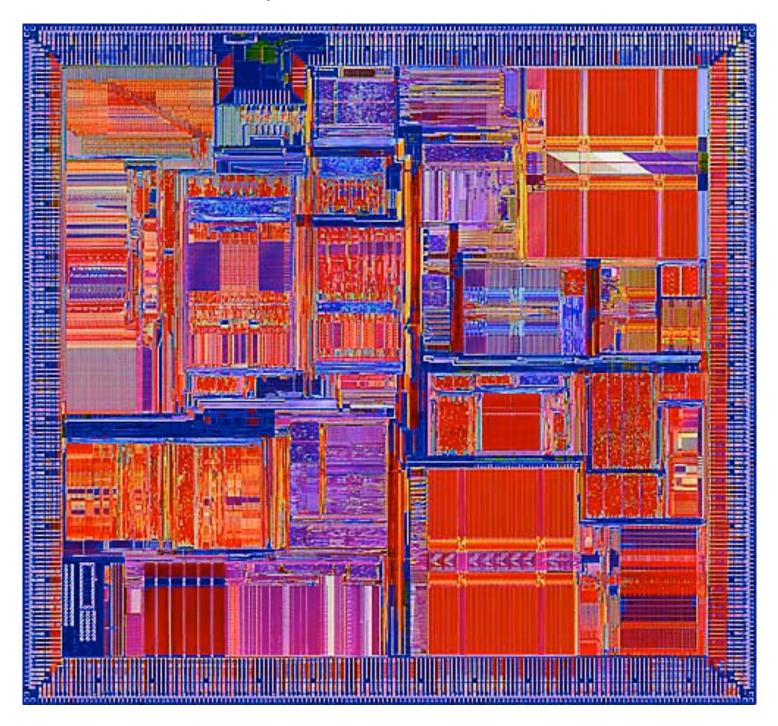

# Real Microprocessor (MIPS R10000)

# Layers of Abstraction

| Abstraction           | Built From                                | Examples                            |

|-----------------------|-------------------------------------------|-------------------------------------|

| Abstract Switch       | raw materials                             | transistor, relay                   |

| Connector             | raw materials                             | wire                                |

| Clock                 | raw materials                             | crystal oscillator                  |

| Logic Gates           | abstract switches,<br>connectors          | AND, OR, NOT                        |

| Combinational Circuit | logic gates, connectors                   | decoder, multiplexer,<br>adder      |

| Sequential Circuit    | logic gates, clock,<br>connector          | flip-flop                           |

| Components            | decoder, multiplexer,<br>adder, flip-flop | registers, ALU,<br>counter, control |

| Computer              | components                                | ТОУ                                 |

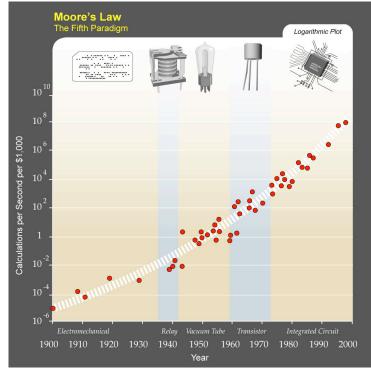

# History + Future

#### Computer constructed by layering abstractions.

- Better implementation at low levels improves everything.

- Ongoing search for better abstract switch!

#### History.

- 1820s: mechanical switches.

- 1940s: relays, vacuum tubes.

- 1950s: transistor, core memory.

- 1960s: integrated circuit.

- 1970s: microprocessor.

- 1980s: VLSI.

- 1990s: integrated systems.

- 2000s: web computer.

- Future: quantum, optical soliton, ...