# 6. Combinational Circuits

George Boole (1815 - 1864)

Claude Shannon (1916 - 2001)

#### Q. What is a digital system?

- A. Digital: signals are 0 or 1.

- Q. Why digital systems?

- A. Accurate, reliable, fast, cheap.

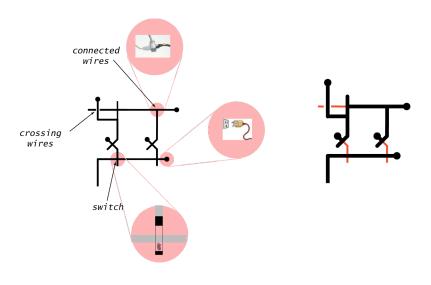

#### Basic abstractions.

- On, off.

- Wire: propagates on/off value.

- Switch: controls propagation of on/off values through wires.

Applications. Cell phone, iPod, antilock brakes, microprocessors, ...

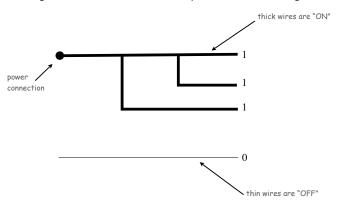

Wires

2

4

# **Building Blocks**

#### Wires.

- ON (1): connected to power.

- OFF (0): not connected to power.

- If a wire is connected to a wire that is on, that wire is also on.

- Typical drawing convention: "flow" from top, left to bottom, right.

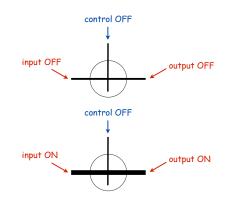

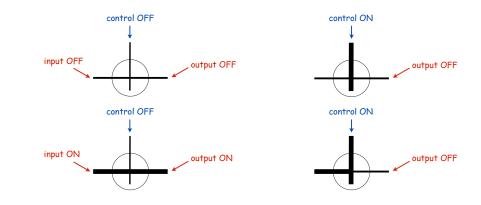

# Controlled Switch

#### Controlled switch.

• 3 connections: input, output, control.

#### Controlled switch.

- 3 connections: input, output, control.

- control OFF: output is connected to input

Controlled Switch

### Controlled switch.

- 3 connections: input, output, control.

- control ON: output is disconnected from input

Controlled Switch

#### Controlled switch.

- 3 connections: input, output, control.

- control OFF: output is connected to input

- control ON: output is disconnected from input

idealized model of "pass transistors" found in real integrated circuits

8

output OFF

output OFF

5

control ON

control ON

## Relay implementation.

- 3 connections: input, output, control.

- Magnetic force pulls on a contact that cuts electrical flow.

Anatomy of a relay (controlled switch)

First Level of Abstraction

## Separates physical world from logical world.

- we assume that switches operate as specified

- that is the only assumption

- physical realization of switch is irrelevant to design

## Physical realization dictates performance

- size

- speed

- power

New technology immediately gives new computer.

Better switch? Better computer.

Controlled Switches: A First Level of Abstraction

## Some amusing attempts to prove the point:

| Technology | "Information"      | Switch |

|------------|--------------------|--------|

| pneumatic  | air pressure       |        |

| fluid      | water pressure     |        |

| relay      | electric potential |        |

Controlled Switches: A First Level of Abstraction

# Real-world examples that prove the point:

| technology                                 | switch      |

|--------------------------------------------|-------------|

| relay                                      | 1 Alexandre |

| vacuum tube                                |             |

| transistor                                 |             |

| "pass transistor" in<br>integrated circuit |             |

| atom-thick transistor                      |             |

9

# VLSI = Very Large Scale Integration

Technology: Deposit materials on substrate.

Key property: Crossing lines are controlled switches.

Key challenge in physical world: Fabricating physical circuits with billions of controlled switches

Key challenge in "abstract" world: Understanding behavior of circuits with billions of controlled switches

Bottom line: Circuit = Drawing (!)

13

need more "levels of abstraction" to understand circuit behavior

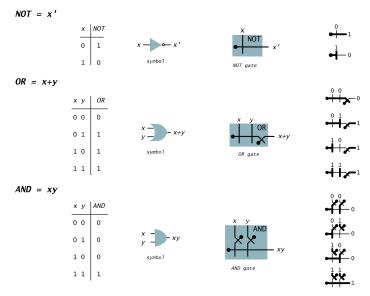

# Second Level of Abstraction: Logic Gates

# Second Level of Abstraction: Logic Gates

implementations with switches

16

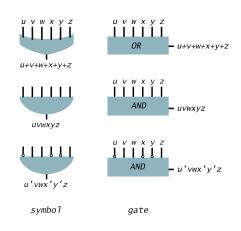

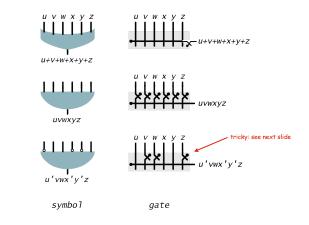

## Multiway Gates

#### Multiway gates.

- OR: 1 if any input is 1; 0 otherwise.

- AND: 1 if all inputs are 1; 0 otherwise.

- Generalized: negate some inputs.

Building blocks (summary)

#### Wires

Controlled switches

#### Gates

Generalized multiway gates

AND gate

implementation

011001

interpretation: value is 1 iff variables

with inverters

19

17

simpler version underlying circuit

## Multiway gates.

- OR: 1 if any input is 1; 0 otherwise.

- AND: 1 if all inputs are 1; 0 otherwise.

- Generalized: negate some inputs.

18

# Boolean Algebra

Boolean Algebra

#### History.

- Developed by Boole to solve mathematical logic problems (1847).

- Shannon master's thesis applied it to digital circuits (1937).

\* "possibly the most important, and also the most famous, master's thesis of the [20th] century" – Howard Gardner

## Boolean algebra.

- Boolean variable: value is 0 or 1.

- Boolean function: function whose inputs and outputs are 0, 1.

## Relationship to circuits.

- Boolean variable: signal.

- Boolean function: circuit.

## Truth Table

#### Truth table.

- Systematic method to describe Boolean function.

- One row for each possible input combination.

0

0

1

1 1

0

1

0

AND truth table

0

0

0

1

• *n* inputs  $\Rightarrow 2^n$  rows.

Boole Orders Lunch

Copyright 2004, Sidney Harris http://www.sciencecartoonsplus.com

22

# Truth Table for Functions of 2 Variables

#### Truth table.

• 16 Boolean functions of 2 variables.

- every 4-bit value represents one

| x | у | ZERO | AND |   | x |   | у | XOR | OR |

|---|---|------|-----|---|---|---|---|-----|----|

| 0 | 0 | 0    | 0   | 0 | 0 | 0 | 0 | 0   | 0  |

| 0 | 1 | 0    | 0   | 0 | 0 | 1 | 1 | 1   | 1  |

| 1 | 0 | 0    | 0   | 1 | 1 | 0 | 0 | 1   | 1  |

| 1 | 1 | 0    | 1   | 0 | 1 | 0 | 1 | 0   | 1  |

truth table for all Boolean functions of 2 variables

| x | у | NOR | EQ | y' |   | <i>x</i> ' |   | NAND | ONE |

|---|---|-----|----|----|---|------------|---|------|-----|

| 0 | 0 | 1   | 1  | 1  | 1 | 1          | 1 | 1    | 1   |

| 0 | 1 | 0   | 0  | 0  | 0 | 1          | 1 | 1    | 1   |

| 1 | 0 | 0   | 0  | 1  | 1 | 0          | 0 | 1    | 1   |

| 1 | 1 | 0   | 1  | 0  | 1 | 0          | 1 | 0    | 1   |

truth table for all Boolean functions of 2 variables

## Truth table.

- 16 Boolean functions of 2 variables.

- 256 Boolean functions of 3 variables.

- 2<sup>(2</sup><sup>n</sup>) Boolean functions of *n* variables!

every 4-bit value represents one - every 8-bit value represents one

every 2<sup>n</sup>-bit value represents one

are universal

#### Fact. Any Boolean function can be expressed using AND, OR, NOT.

- { AND, OR, NOT } are universal.

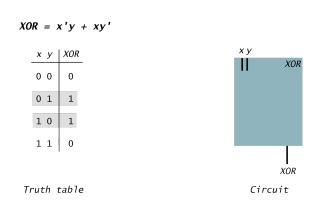

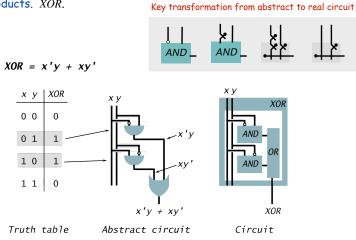

- Ex: XOR(x, y) = xy' + x'y.

| notation   | meaning |

|------------|---------|

| <i>x</i> ' | NOT x   |

| x y        | x AND y |

| x + y      | x OR y  |

26

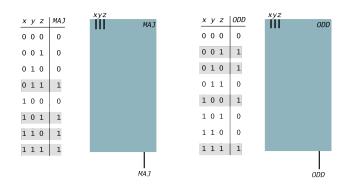

|   | ¢ | у | z | AND | OR | MAJ | ODD |

|---|---|---|---|-----|----|-----|-----|

| ( | ) | 0 | 0 | 0   | 0  | 0   | 0   |

| ( | ) | 0 | 1 | 0   | 1  | 0   | 1   |

| ( | ) | 1 | 0 | 0   | 1  | 0   | 1   |

| ( | ) | 1 | 1 | 0   | 1  | 1   | 0   |

| 1 | L | 0 | 0 | 0   | 1  | 0   | 1   |

| 1 | L | 0 | 1 | 0   | 1  | 1   | 0   |

| 1 | L | 1 | 0 | 0   | 1  | 1   | 0   |

| 1 | L | 1 | 1 | 1   | 1  | 1   | 1   |

some functions of 3 variables

## Sum-of-Products

| Sum-of-products. Systematic procedure for represent | nting a Boolean              |

|-----------------------------------------------------|------------------------------|

| function using AND, OR, NOT.                        | Υ.                           |

| • Form AND term for each 1 in Poolean function      | proves that { AND, OR, NOT } |

- Form AND term for each 1 in Boolean function.

- OR terms together.

| x | у | z | MAJ | x'yz | xy'z | xyz' | xyz | x'yz + xy'z + xyz' + xyz |

|---|---|---|-----|------|------|------|-----|--------------------------|

| 0 | 0 | 0 | 0   | 0    | 0    | 0    | 0   | 0                        |

| 0 | 0 | 1 | 0   | 0    | 0    | 0    | 0   | 0                        |

| 0 | 1 | 0 | 0   | 0    | 0    | 0    | 0   | 0                        |

| 0 | 1 | 1 | 1   | 1    | 0    | 0    | 0   | 1                        |

| 1 | 0 | 0 | 0   | 0    | 0    | 0    | 0   | 0                        |

| 1 | 0 | 1 | 1   | 0    | 1    | 0    | 0   | 1                        |

| 1 | 1 | 0 | 1   | 0    | 0    | 1    | 0   | 1                        |

| 1 | 1 | 1 | 1   | 0    | 0    | 0    | 1   | 1                        |

expressing *MAJ* using sum-of-products

| Expressing | XOR | Using | AND, | OR, | NOT |

|------------|-----|-------|------|-----|-----|

| x | у | <i>x</i> ' | y' | x'y | xy' | x'y + xy' | x XOR y |

|---|---|------------|----|-----|-----|-----------|---------|

| 0 | 0 | 1          | 1  | 0   | 0   | 0         | 0       |

| 0 | 1 | 1          | 0  | 1   | 0   | 1         | 1       |

| 1 | 0 | 0          | 1  | 0   | 1   | 1         | 1       |

| 1 | 1 | 0          | 0  | 0   | 0   | 0         | 0       |

Exercise. Show {AND, NOT}, {OR, NOT}, {NAND} are universal. Hint. DeMorgan's law: (x'y')' = x + y.

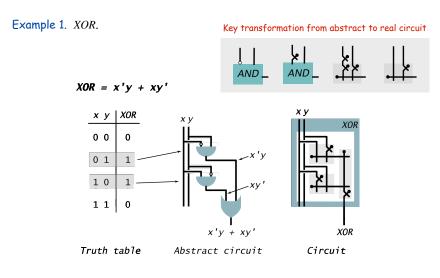

Translate Boolean Formula to Boolean Circuit

#### Sum-of-products. XOR.

# Translate Boolean Formula to Boolean Circuit

Translate Boolean Formula to Boolean Circuit

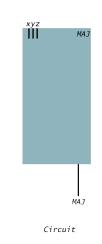

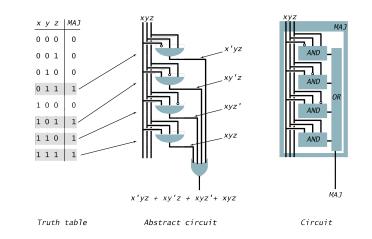

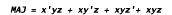

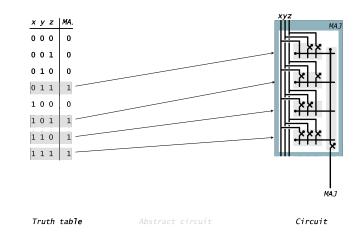

## Example 2. Majority.

MAJ = x'yz + xy'z + xyz' + xyz

Translate Boolean Formula to Boolean Circuit

#### Example 2. Majority.

MAJ = x'yz + xy'z + xyz' + xyz

29

### Example 2. Majority.

MAJ = x'yz + xy'z + xyz' + xyz

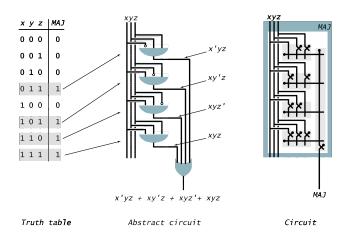

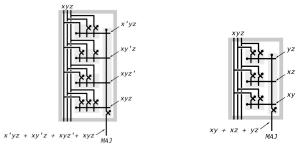

Simplification Using Boolean Algebra

#### Many possible circuits for each Boolean function.

- Sum-of-products not necessarily optimal in:

- number of switches (space)

- depth of circuit (time)

**Ex.** MAJ(x, y, z) = x'yz + xy'z + xyz' + xyz = xy + yz + xz.

size = 10, depth = 2

35

33

## Example 2. Majority.

Combinational Circuit Design: Summary

Problem: Compute the value of a boolean function

#### Ingredients.

- AND gates.

- OR gates.

- NOT gates.

- Wire.

#### Instructions.

- Step 1: represent input and output signals with Boolean variables.

- Step 2: construct truth table to carry out computation.

- Step 3: derive (simplified) Boolean expression using sum-of products.

- Step 4: transform Boolean expression into circuit.

# Bottom line (profound idea):

It is easy to design a circuit to compute ANY boolean function.

Caveat (stay tuned): Circuit might be huge.

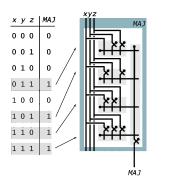

# Example 3. Odd parity

- 1 if odd number of inputs are 1.

- 0 otherwise.

|   |   |   | $\checkmark$ |       |       |       |     | $\rightarrow$               |

|---|---|---|--------------|-------|-------|-------|-----|-----------------------------|

| x | у | z | ODD          | x'y'z | x'yz' | xy'z' | xyz | x'y'z + x'yz' + xy'z' + xyz |

| 0 | 0 | 0 | 0            | 0     | 0     | 0     | 0   | 0                           |

| 0 | 0 | 1 | 1            | 1     | 0     | 0     | 0   | 1                           |

| 0 | 1 | 0 | 1            | 0     | 1     | 0     | 0   | 1                           |

| 0 | 1 | 1 | 0            | 0     | 0     | 0     | 0   | 0                           |

| 1 | 0 | 0 | 1            | 0     | 0     | 1     | 0   | 1                           |

| 1 | 0 | 1 | 0            | 0     | 0     | 0     | 0   | 0                           |

| 1 | 1 | 0 | 0            | 0     | 0     | 0     | 0   | 0                           |

| 1 | 1 | 1 | 1            | 0     | 0     | 0     | 1   | 1                           |

Expressing ODD using sum-of-products

Translate Boolean Formula to Boolean Circuit

# Example 3. Odd parity

- 1 if odd number of inputs are 1.

- 0 otherwise.

MAJ = x'yz + xy'z + xyz' + xyz ODD = x'y'z + x'yz' + xy'z' + xyz

Translate Boolean Formula to Boolean Circuit

# Example 3. Odd parity

- 1 if odd number of inputs are 1.

- 0 otherwise.

MAJ = x'yz + xy'z + xyz' + xyz

ODD = x'y'z + x'yz' + xy'z' + xyz

38

Adder Circuit

## Let's Make an Adder Circuit

## Let's Make an Adder Circuit

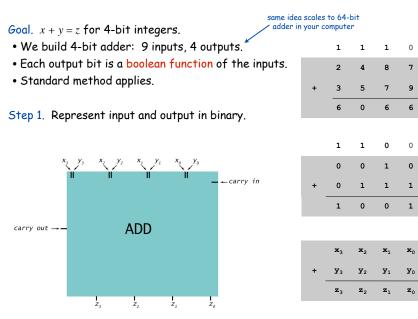

#### Goal. x + y = z for 4-bit integers.

#### Step 2. Do one bit at a time!

- Build truth table for carry bit.

- Build truth table for summand bit.

| carry bit      |                |                |           |  |  |  |  |  |  |  |

|----------------|----------------|----------------|-----------|--|--|--|--|--|--|--|

| x <sub>i</sub> | y <sub>i</sub> | c <sub>i</sub> | $c_{i+I}$ |  |  |  |  |  |  |  |

| 0              | 0              | 0              | 0         |  |  |  |  |  |  |  |

| 0              | 0              | 1              | 0         |  |  |  |  |  |  |  |

| 0              | 1              | 0              | 0         |  |  |  |  |  |  |  |

| 0              | 1              | 1              | 1         |  |  |  |  |  |  |  |

| 1              | 0              | 0              | 0         |  |  |  |  |  |  |  |

| 1              | 0              | 1              | 1         |  |  |  |  |  |  |  |

| 1              | 1              | 0              | 1         |  |  |  |  |  |  |  |

| 1              | 1              | 1              | 1         |  |  |  |  |  |  |  |

| $\mathbf{c}_{\mathtt{out}}$ | c3         | C2                    | c <sub>1</sub> | $c_0 = 0$             |

|-----------------------------|------------|-----------------------|----------------|-----------------------|

|                             | <b>x</b> 3 | <b>x</b> <sub>2</sub> | <b>x</b> 1     | $\mathbf{x}_{0}$      |

| +                           | <b>Y</b> 3 | <b>Y</b> 2            | <b>y</b> 1     | <b>Y</b> 0            |

|                             | <b>z</b> 3 | z <sub>2</sub>        | $\mathbf{z}_1$ | <b>z</b> <sub>0</sub> |

| summand bit    |                |                |       |  |  |  |  |  |  |

|----------------|----------------|----------------|-------|--|--|--|--|--|--|

| x <sub>i</sub> | y <sub>i</sub> | c <sub>i</sub> | $z_i$ |  |  |  |  |  |  |

| 0              | 0              | 0              | 0     |  |  |  |  |  |  |

| 0              | 0              | 1              | 1     |  |  |  |  |  |  |

| 0              | 1              | 0              | 1     |  |  |  |  |  |  |

| 0              | 1              | 1              | 0     |  |  |  |  |  |  |

| 1              | 0              | 0              | 1     |  |  |  |  |  |  |

| 1              | 0              | 1              | 0     |  |  |  |  |  |  |

| 1              | 1              | 0              | 0     |  |  |  |  |  |  |

| 1              | 1              | 1              | 1     |  |  |  |  |  |  |

## Let's Make an Adder Circuit

| Goal. $x + y = z$ for 4-bit integers.                                | $\mathbf{c}_{\mathtt{out}}$ |  |                       |                | ${\tt c}_{\tt in}$ |

|----------------------------------------------------------------------|-----------------------------|--|-----------------------|----------------|--------------------|

| <ul><li>Step 2. [first attempt]</li><li>Build truth table.</li></ul> | +                           |  | -                     | -              | Ŭ                  |

| • Build fruth Table.                                                 |                             |  | <b>z</b> <sub>2</sub> | $\mathbf{z}_1$ | $\mathbf{z}_0$     |

|   | 4-bit adder truth table |                       |                       |                |                       |            |                       |            |    |       |       |       |       |                              |

|---|-------------------------|-----------------------|-----------------------|----------------|-----------------------|------------|-----------------------|------------|----|-------|-------|-------|-------|------------------------------|

|   | $c_0$                   | <i>x</i> <sub>3</sub> | <i>x</i> <sub>2</sub> | x <sub>I</sub> | <i>x</i> <sub>0</sub> | <i>y</i> 3 | <i>y</i> <sub>2</sub> | <i>y</i> 1 | Уо | $z_3$ | $z_2$ | $z_I$ | $z_0$ |                              |

| İ | 0                       | 0                     | 0                     | 0              | 0                     | 0          | 0                     | 0          | 0  | 0     | 0     | 0     | 0     |                              |

|   | 0                       | 0                     | 0                     | 0              | 0                     | 0          | 0                     | 0          | 1  | 0     | 0     | 0     | 1     |                              |

|   | 0                       | 0                     | 0                     | 0              | 0                     | 0          | 0                     | 1          | 0  | 0     | 0     | 1     | 0     |                              |

| ĺ | 0                       | 0                     | 0                     | 0              | 0                     | 0          | 0                     | 1          | 1  | 0     | 0     | 1     | 1     | 2 <sup>8+1</sup> = 512 rows! |

|   | 0                       | 0                     | 0                     | 0              | 0                     | 0          | 1                     | 0          | 0  | 0     | 1     | 0     | 0     |                              |

| ĺ |                         |                       |                       |                |                       |            |                       |            |    |       |       |       |       |                              |

| ĺ | 1                       | 1                     | 1                     | 1              | 1                     | 1          | 1                     | 1          | 1  | 1     | 1     | 1     | 1     |                              |

Q. Why is this a bad idea?

## Let's Make an Adder Circuit

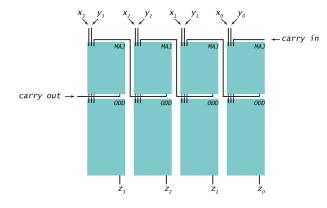

#### Step 3. A surprise!

- carry bit is majority function

- summand bit is odd parity function.

| $\mathbf{c}_{\mathtt{out}}$ | c3                    | c <sub>2</sub>        | c1         | $\mathbf{c}_0 = 0$    |

|-----------------------------|-----------------------|-----------------------|------------|-----------------------|

|                             | <b>x</b> 33           | <b>x</b> <sub>2</sub> | <b>x</b> 1 | <b>x</b> <sub>0</sub> |

| +                           | <b>y</b> 3            | <b>Y</b> 2            | <b>Y</b> 1 | <b>Y</b> 0            |

|                             | <b>z</b> <sub>3</sub> | <b>z</b> <sub>2</sub> | <b>z</b> 1 | <b>z</b> <sub>0</sub> |

42

| carry bit      |                |                |           |     |  |  |  |  |  |  |

|----------------|----------------|----------------|-----------|-----|--|--|--|--|--|--|

| x <sub>i</sub> | y <sub>i</sub> | c <sub>i</sub> | $c_{i+I}$ | MAJ |  |  |  |  |  |  |

| 0              | 0              | 0              | 0         | 0   |  |  |  |  |  |  |

| 0              | 0              | 1              | 0         | 0   |  |  |  |  |  |  |

| 0              | 1              | 0              | 0         | 0   |  |  |  |  |  |  |

| 0              | 1              | 1              | 1         | 1   |  |  |  |  |  |  |

| 1              | 0              | 0              | 0         | 0   |  |  |  |  |  |  |

| 1              | 0              | 1              | 1         | 1   |  |  |  |  |  |  |

| 1              | 1              | 0              | 1         | 1   |  |  |  |  |  |  |

| 1              | 1              | 1              | 1         | 1   |  |  |  |  |  |  |

|                |                |                |           |     |  |  |  |  |  |  |

0

7

9

0

0

1

1

x<sub>0</sub>

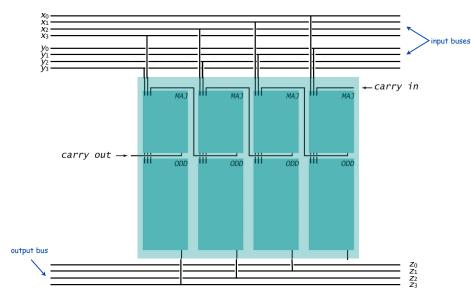

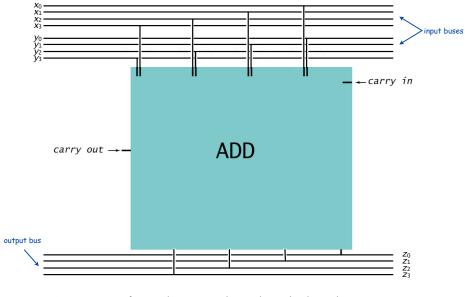

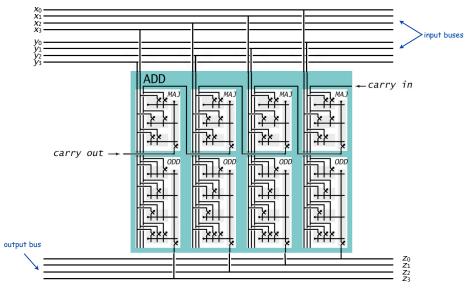

Adder: Interface

#### Goal. x + y = z for 4-bit integers.

#### Step 4.

- Transform Boolean expression into circuit (use known components!).

- Chain together 1-bit adders.

- That's it!

## Adder: Component Level View

45

A bus is a group of wires that connect (carry data values) to other components.

Adder: Switch Level View

# Useful Combinational Circuits

R. K. K. K.

벏벏뷬

Decoder

Incrementer (easy, add 0001)

Bitwise AND, XOR (easy)

Decoder [next slide]

Shifter (clever, but we'll skip details)

Multiplexer [next lecture]

Decoder

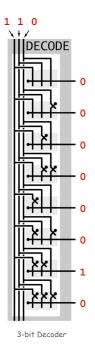

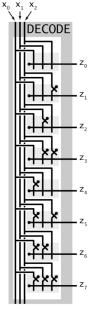

#### Decoder. [n-bit]

- n address inputs, 2<sup>n</sup> data outputs.

- Addressed output bit is 1; others are 0.

- Compact implementation of n Boolean functions

| x <sub>0</sub> | <b>x</b> 1 | <b>x</b> 2 | z, | <b>z</b> 1 | <b>z</b> 2 | <b>z</b> 3 | z4 | <b>z</b> 5 | z <sub>6</sub> | <b>z</b> 7 |

|----------------|------------|------------|----|------------|------------|------------|----|------------|----------------|------------|

| 0              | 0          | 0          | 1  | 0          | 0          | 0          | 0  | 0          | 0              | 0          |

| 0              | 0          | 1          | 0  | 1          | 0          | 0          | 0  | 0          | 0              | 0          |

| 0              | 1          | 0          | 0  | 0          | 1          | 0          | 0  | 0          | 0              | 0          |

| 0              | 1          | 1          | 0  | 0          | 0          | 1          | 0  | 0          | 0              | 0          |

| 1              | 0          | 0          | 0  | 0          | 0          | 0          | 1  | 0          | 0              | 0          |

| 1              | 0          | 1          | 0  | 0          | 0          | 0          | 0  | 1          | 0              | 0          |

| 1              | 1          | 0          | 0  | 0          | 0          | 0          | 0  | 0          | 1              | 0          |

| 1              | 1          | 1          | 0  | 0          | 0          | 0          | 0  | 0          | 0              | 1          |

49

## Decoder. [n-bit]

- n address inputs, 2<sup>n</sup> data outputs.

- Addressed output bit is 1; others are 0.

- Compact implementation of n Boolean functions

| $\mathbf{x}_0$ | <b>x</b> 1 | <b>x</b> 2 | z <sub>0</sub> | <b>z</b> 1 | <b>z</b> 2 | <b>z</b> 3 | z4 | <b>z</b> 5 | z <sub>6</sub> | <b>z</b> 7 |

|----------------|------------|------------|----------------|------------|------------|------------|----|------------|----------------|------------|

| 0              | 0          | 0          | 1              | 0          | 0          | 0          | 0  | 0          | 0              | 0          |

| 0              | 0          | 1          | 0              | 1          | 0          | 0          | 0  | 0          | 0              | 0          |

| 0              | 1          | 0          | 0              | 0          | 1          | 0          | 0  | 0          | 0              | 0          |

| 0              | 1          | 1          | 0              | 0          | 0          | 1          | 0  | 0          | 0              | 0          |

| 1              | 0          | 0          | 0              | 0          | 0          | 0          | 1  | 0          | 0              | 0          |

| 1              | 0          | 1          | 0              | 0          | 0          | 0          | 0  | 1          | 0              | 0          |

| 1              | 1          | 0          | 0              | 0          | 0          | 0          | 0  | 0          | 1              | 0          |

| 1              | 1          | 1          | 0              | 0          | 0          | 0          | 0  | 0          | 0              | 1          |

3-bit Decoder

50

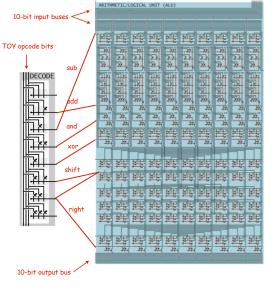

# Decoder application: Your computer's ALU!

#### ALU: Arithmetic and Logic Unit

- implements instructions

- input, output connects

- to registers via buses

### Ex: TOY-Lite (10 bit words)

- 1: add

- 2: subtract

- 3: and

- 4: xor

- 5: shift left

- 6: shift right

#### Details:

- All circuits compute their result.

- Decoder lines AND all results.

- "one-hot" OR collects answer.

# Summary

# Lessons for software design apply to hardware design!

- Interface describes behavior of circuit.

- Implementation gives details of how to build it.

# Layers of abstraction apply with a vengeance!

- On/off.

- Controlled switch. [relay, transistor]

- Gates. [AND, OR, NOT]

- Boolean circuit. [MAJ, ODD]

- Adder.

- Shifter.

- Arithmetic logic unit.

- ...

- TOY machine (stay tuned).

- Your computer.